100进制计数器原理图

74ls90级联实现百进制计数器与清零

数电 计数器

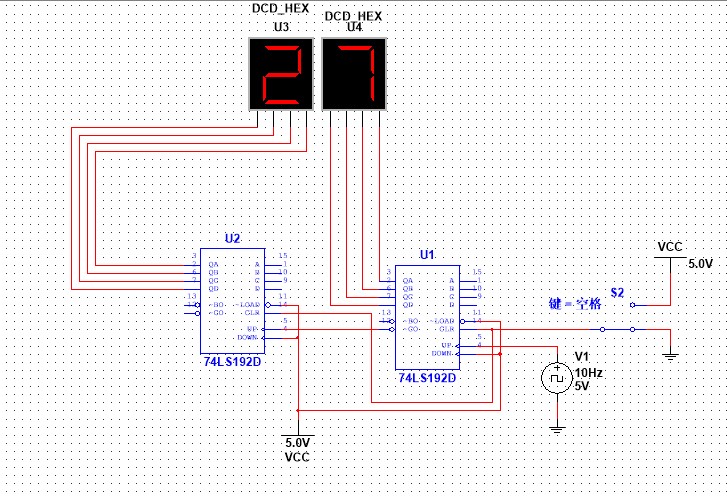

100进制加减计数器电路

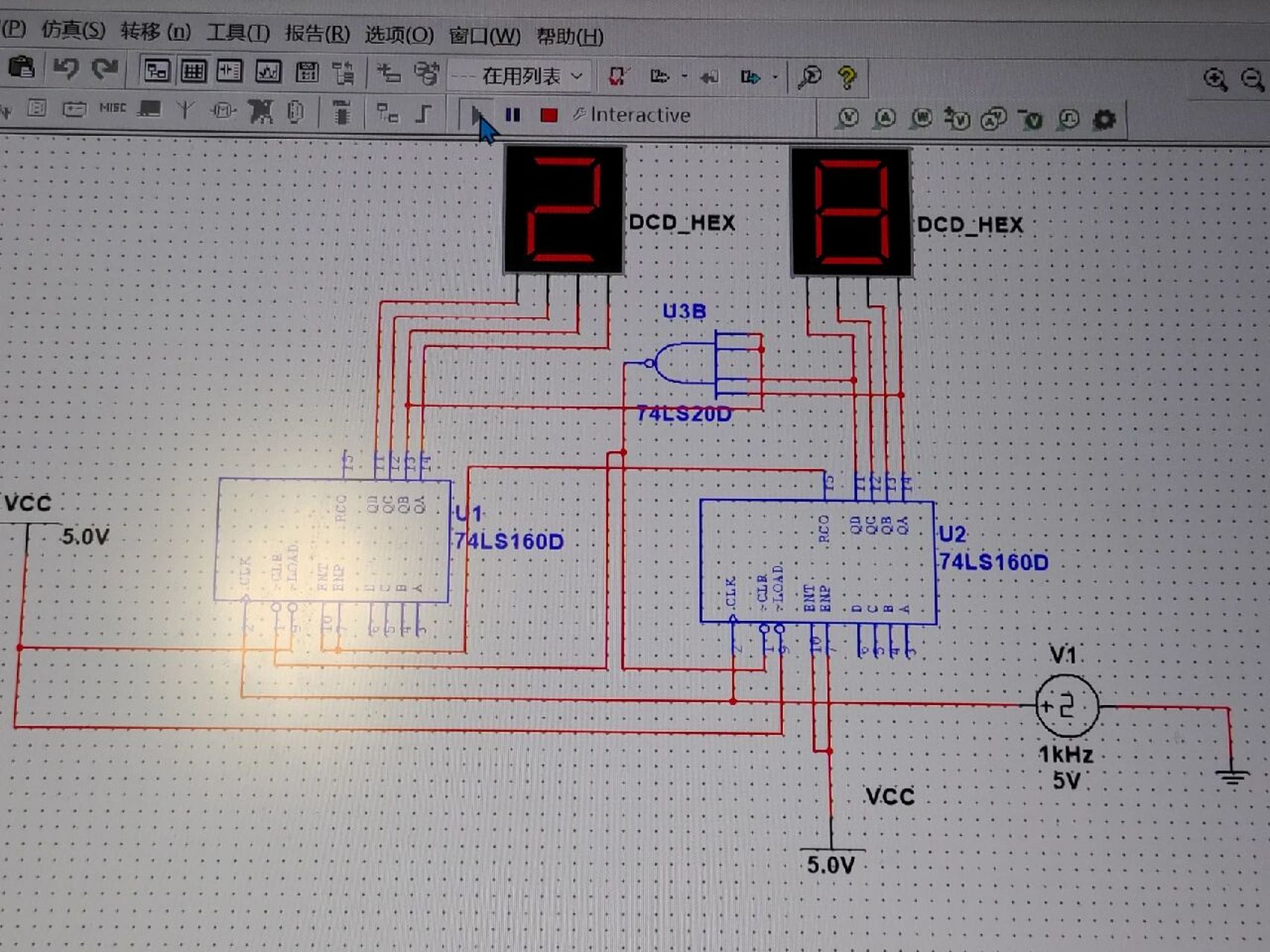

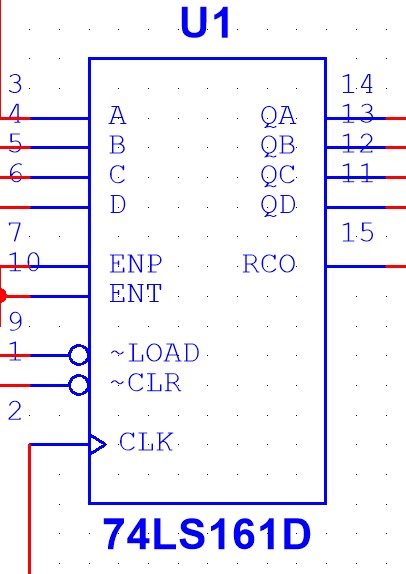

用两片74ls160芯片设计一个的计数器

活动 100进制计数器74161异步清零

74ls90级联实现百进制计数器与清零

100内的加减计数器电路图

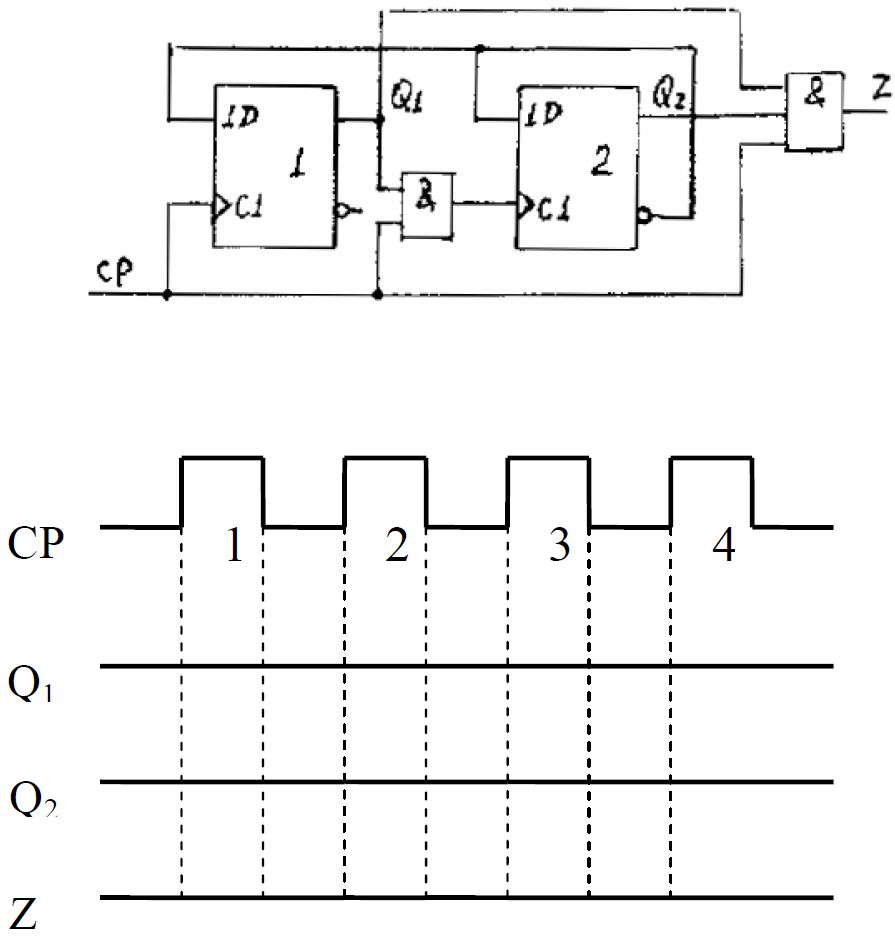

输出波形如下 该电路是三进制计数器

也就是十进制的0到15

由同步十进制加法计数器74ls160构成一数字系统如图所

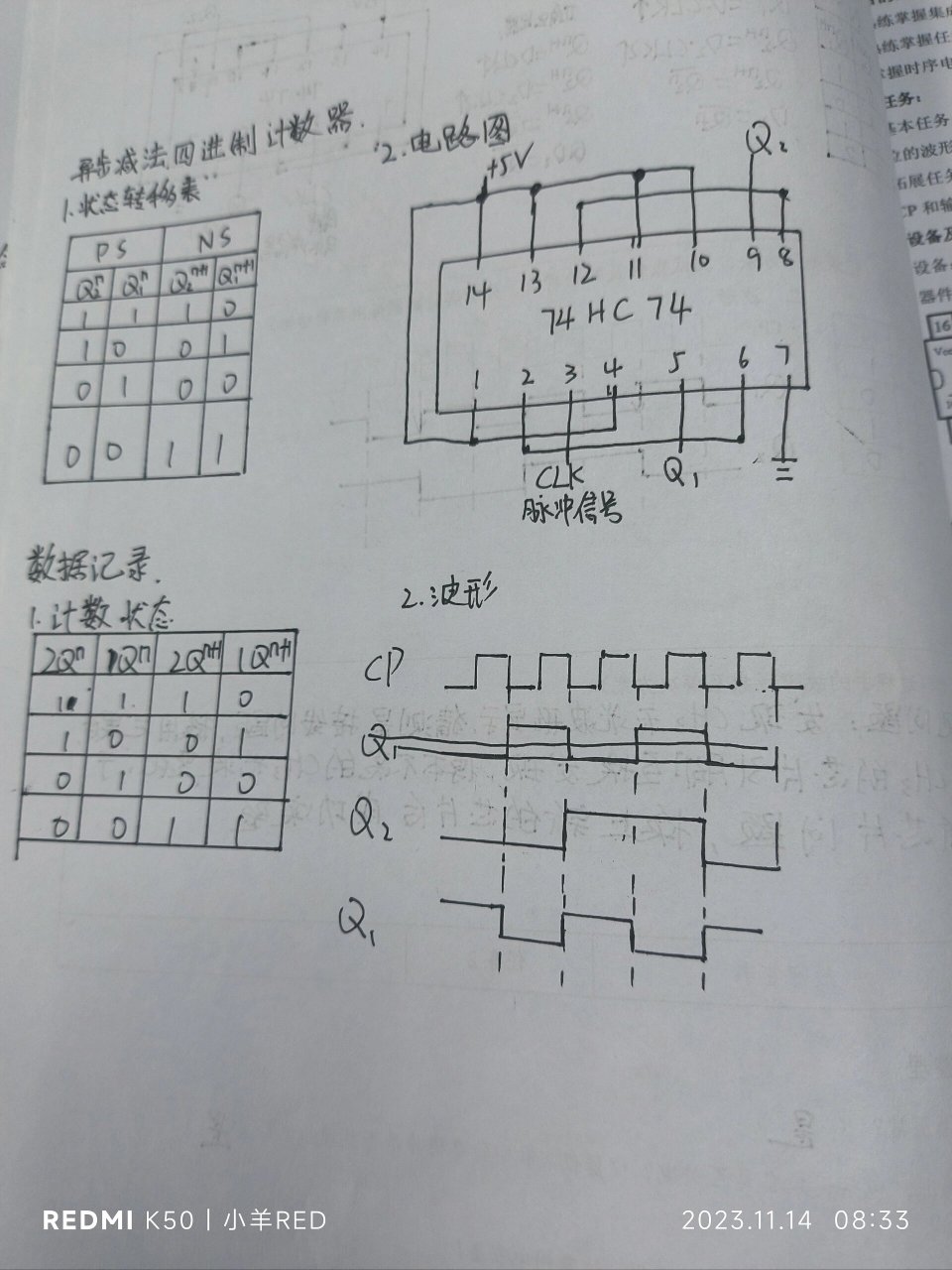

进制计数器电路图

100进制计数器

由源极接地与共基极放大器组合而成的级联式放大器

最新用74390和7448设计100以内任意进制计数器 docx

0仿真应用设计

1

二进制计数

关于数字电路的计数器的问题

可以按自然态序进行计数的n进制计数器的方法

100进制计数器电路图

图6

74ls190级联实现100以内的十进制加/减计数器

终于做出来拉 两片74ls160与一片74ls20构成的29进制计数器

51单片机定时/计数器

一

中央处理器中央处理器是由两个74ls192级联而成100以内的十进制计数器

同步二进制计数器

中央处理器中央处理器是由两个74ls192级联而成100以内的十进制计数器

如何将两个74ls192组成的100进制计数器改为16进制

同步 1 = 异步8 1 使用 74161 异步清零功能设计 n 进制计数器8

电脑版 | 更新时间:2025-02-02 11:09:51