作1010序列检测器的状态图,已知输入,输出序列: 输入

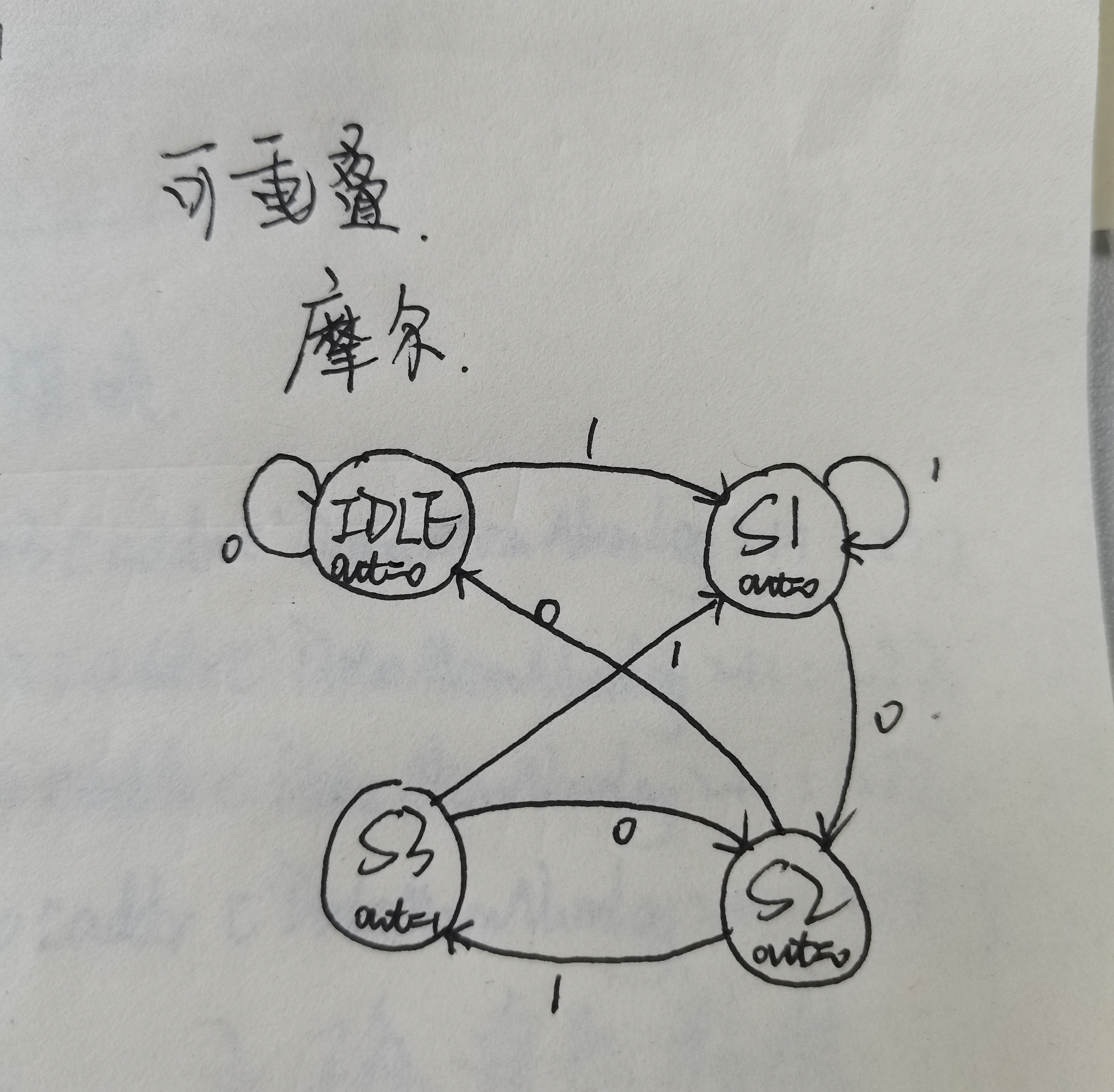

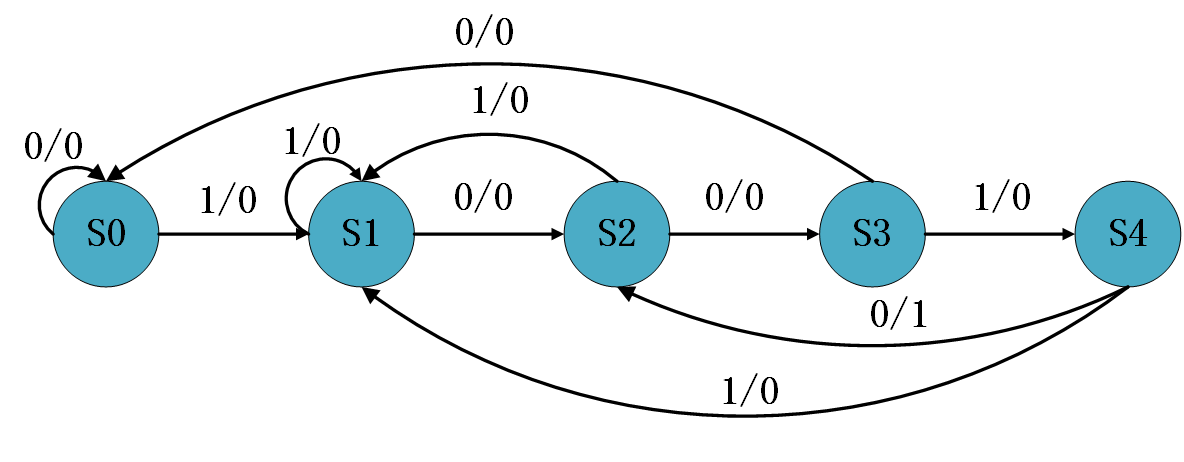

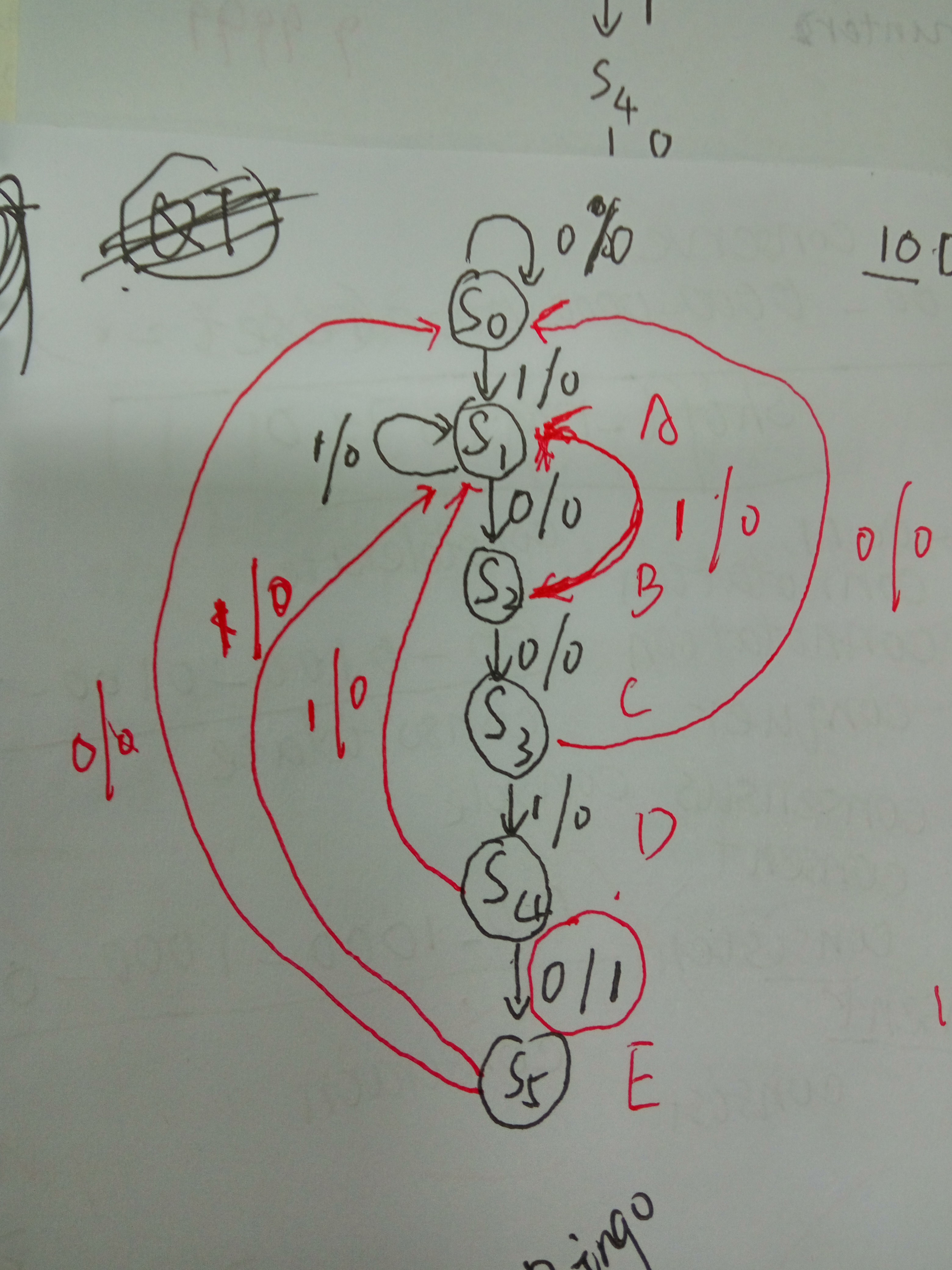

已知不可以重叠检测101序列检测器的输入序列输出序列如下其状态图为

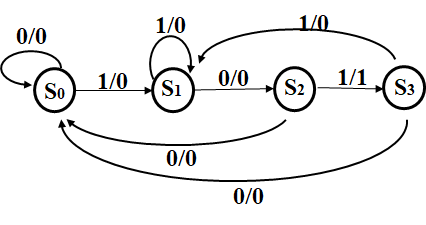

作1010序列检测器的状态图,已知输入,输出序列: 输入

作1010序列检测器的状态图,已知输入,输出序列: 输入

101序列检测器设计

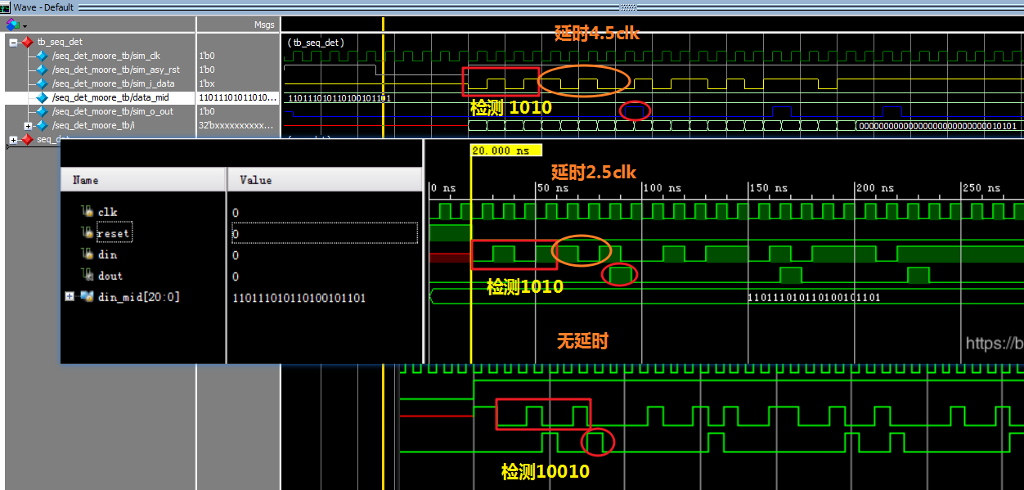

verilog实现101序列检测器moore和mealy型状态机实现可重叠和不可重叠

verilog实现101序列检测器moore和mealy型状态机实现可重叠和不可重叠

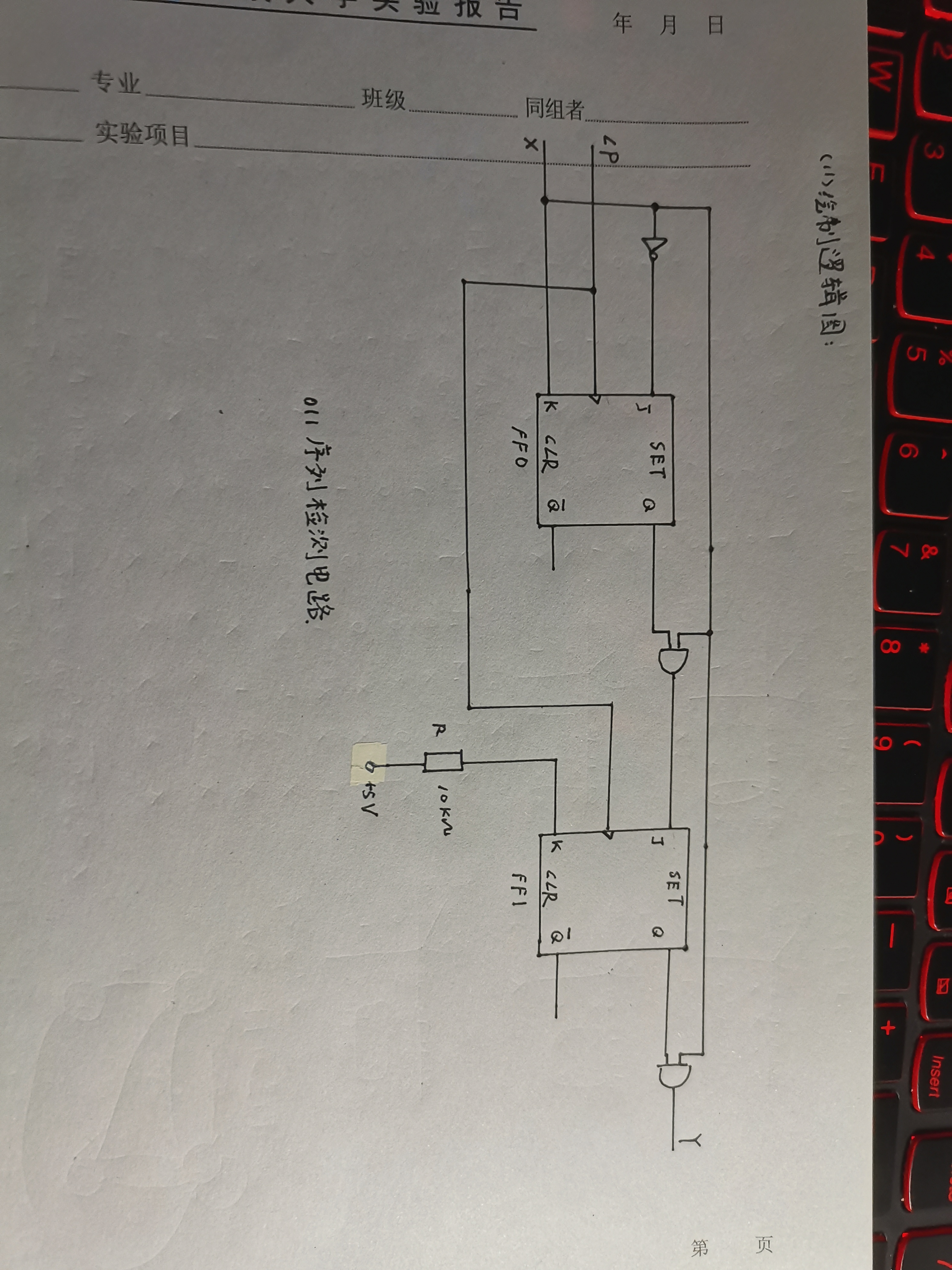

数字逻辑101,011序列状态图

verilog实现101序列检测器moore和mealy型状态机实现可重叠和不可重叠

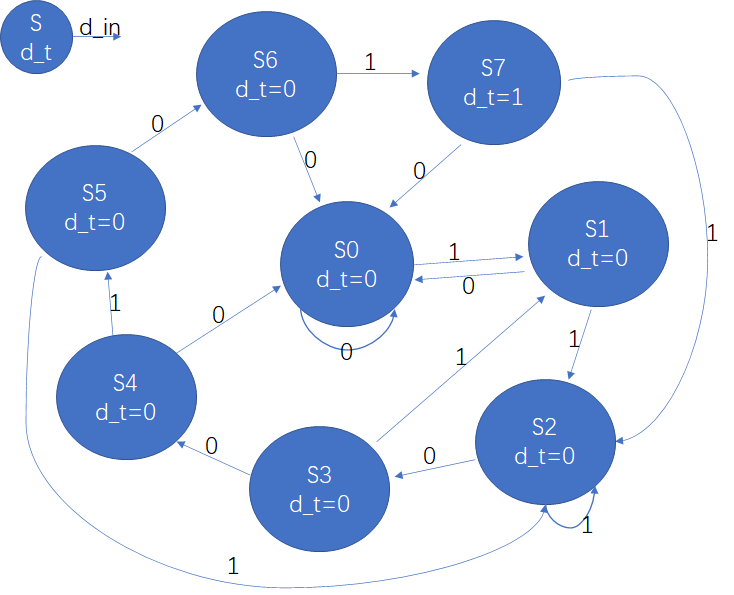

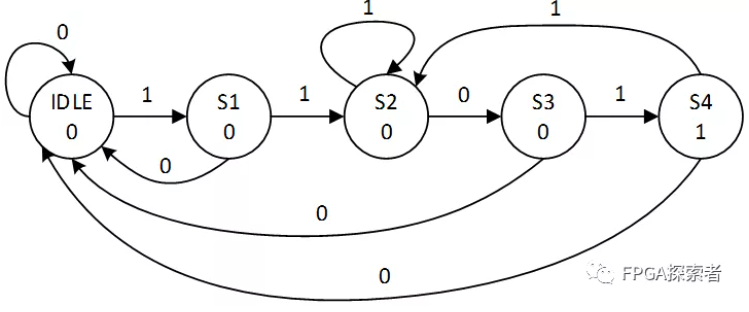

10010序列检测器的状态是7个还是5个?

新手请教如何用状态机实现10010序列检测器

《二进制序列1010检测器正确电路doc》

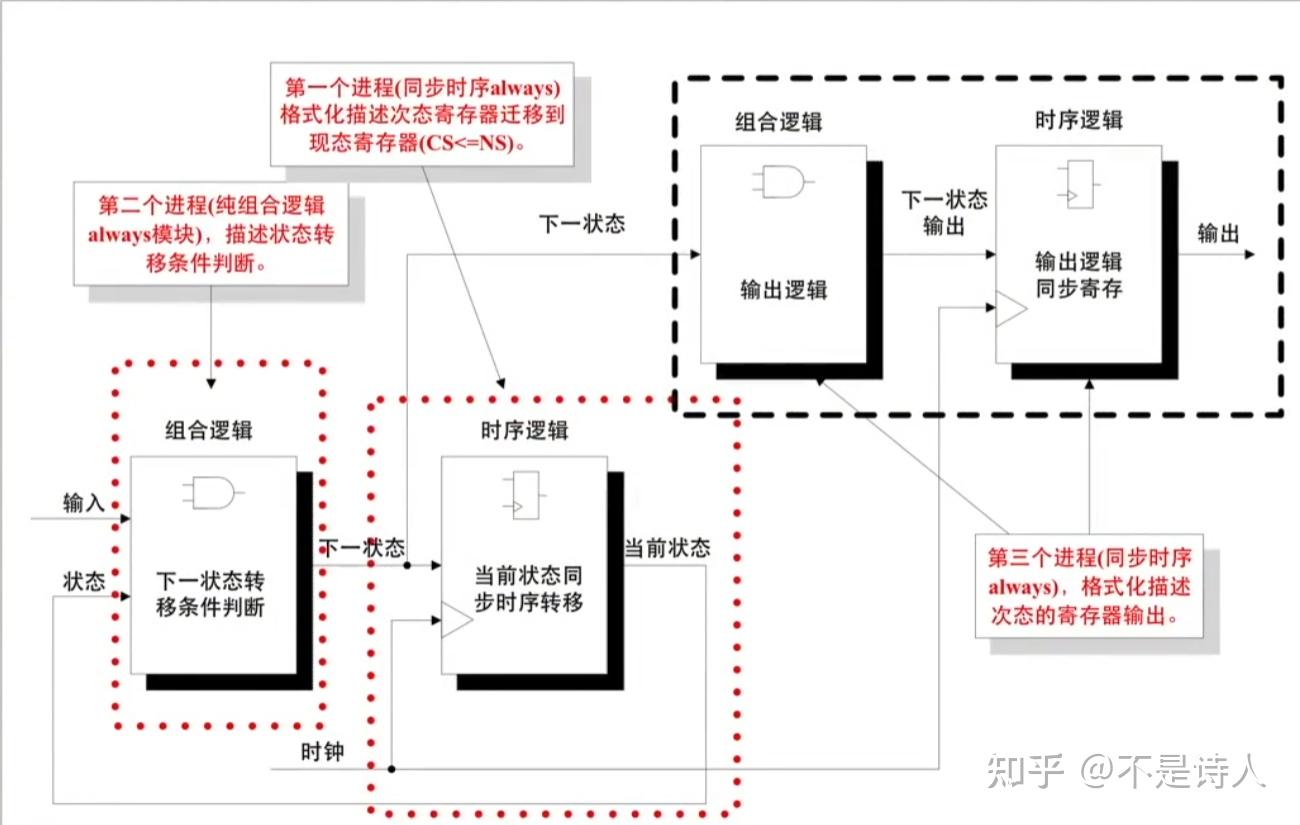

状态机相关知识点(1)

verilog实现101序列检测器moore和mealy型状态机实现可重叠和不可重叠

10010序列检测器

基于psoc编码检测器的设计及实现

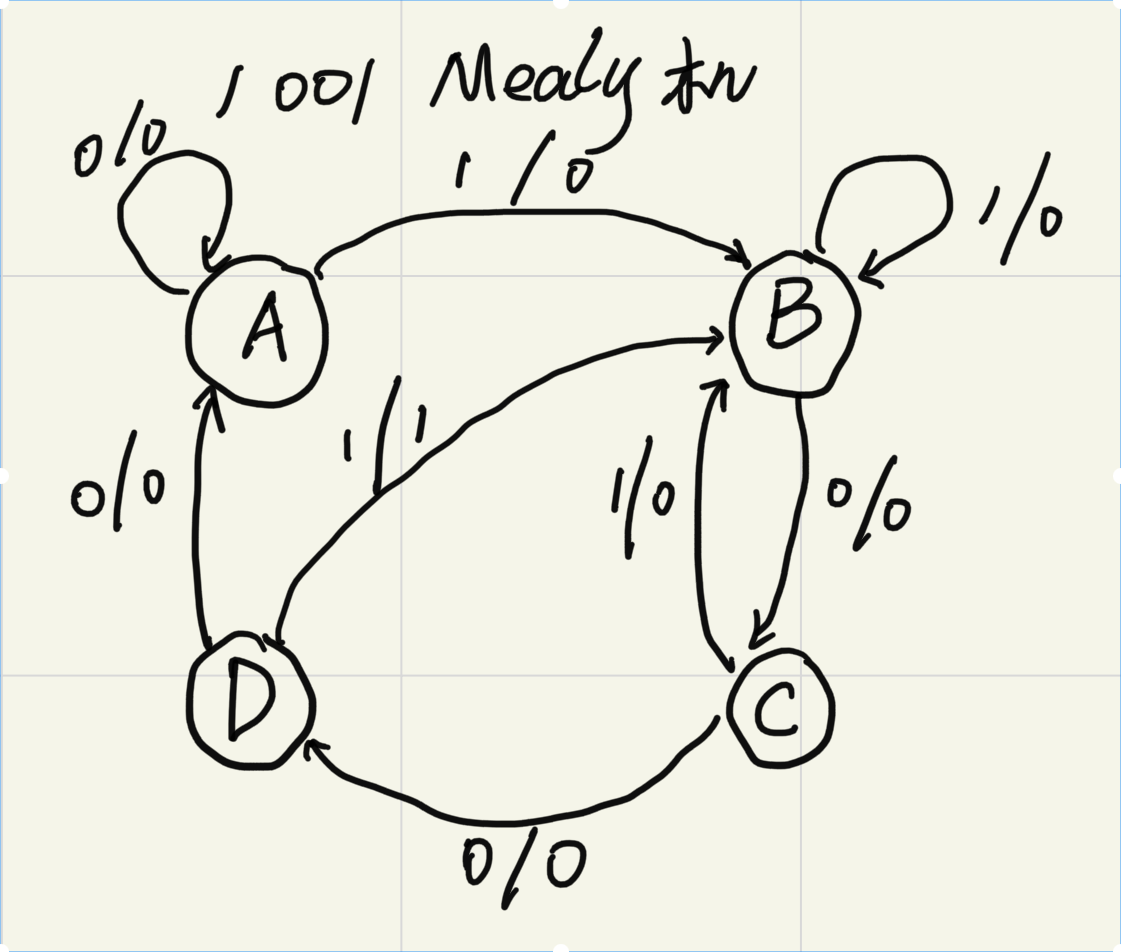

1001序列检测器mealy机状态图以学号最后两位数09为例,09的bcd码为

01111110序列信号检测器的vhdl状态机,状态转换表为什么是这样的,看不

eda设计实验

verilog 序列检测状态机

状态机序列检测器

序列检测器:状态转移图 morrer状态机(三段式) modelsim仿真 – 源码

出现了设计110序列检测器和101序列检测器, 那么今年有可能设计011

fpga电子设计作业:用fsm实现10110串的检测,画出其状态图

数字逻辑1101检测器

用vhdl语言 设计4位序列检测器,当检测到0110时输出1,否则输出0

完整的verilog源代码,仿真通过 用fsm实现101101的序列检测模块

10010序列检测器

1101序列检测

状态转移图21本次设计实现:设计一个10010序列的检测器