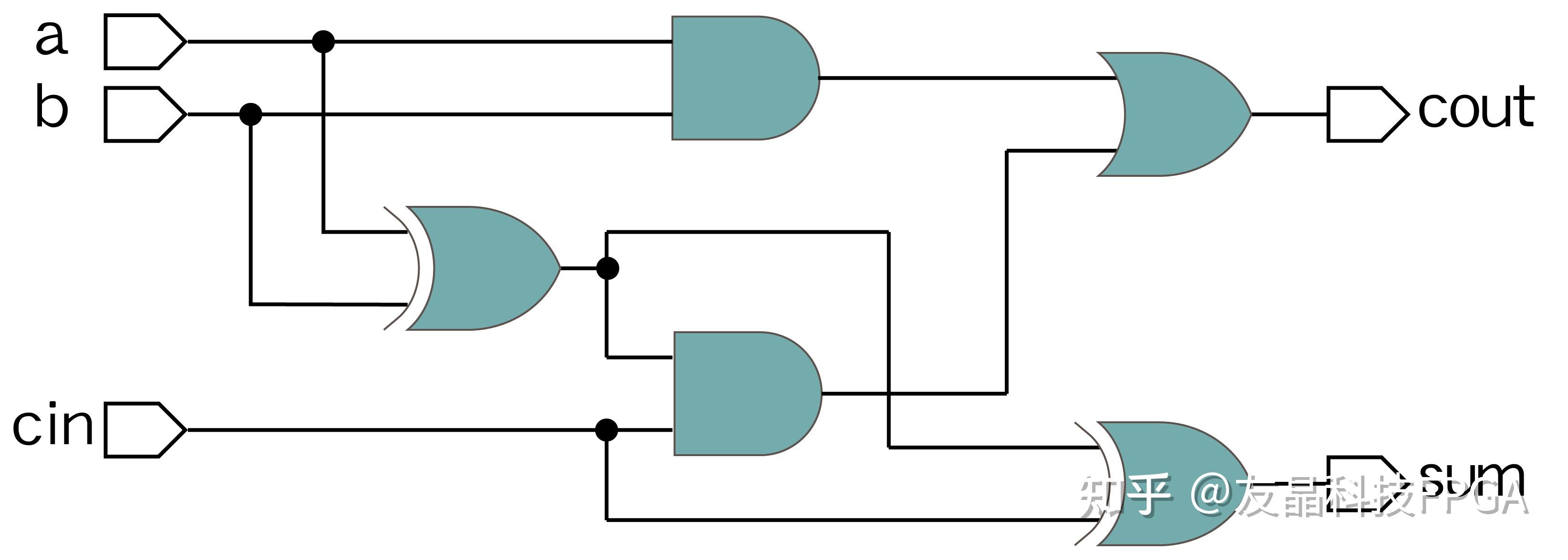

74ls00设计全加器

74ls138译码器

0仿真应用设计

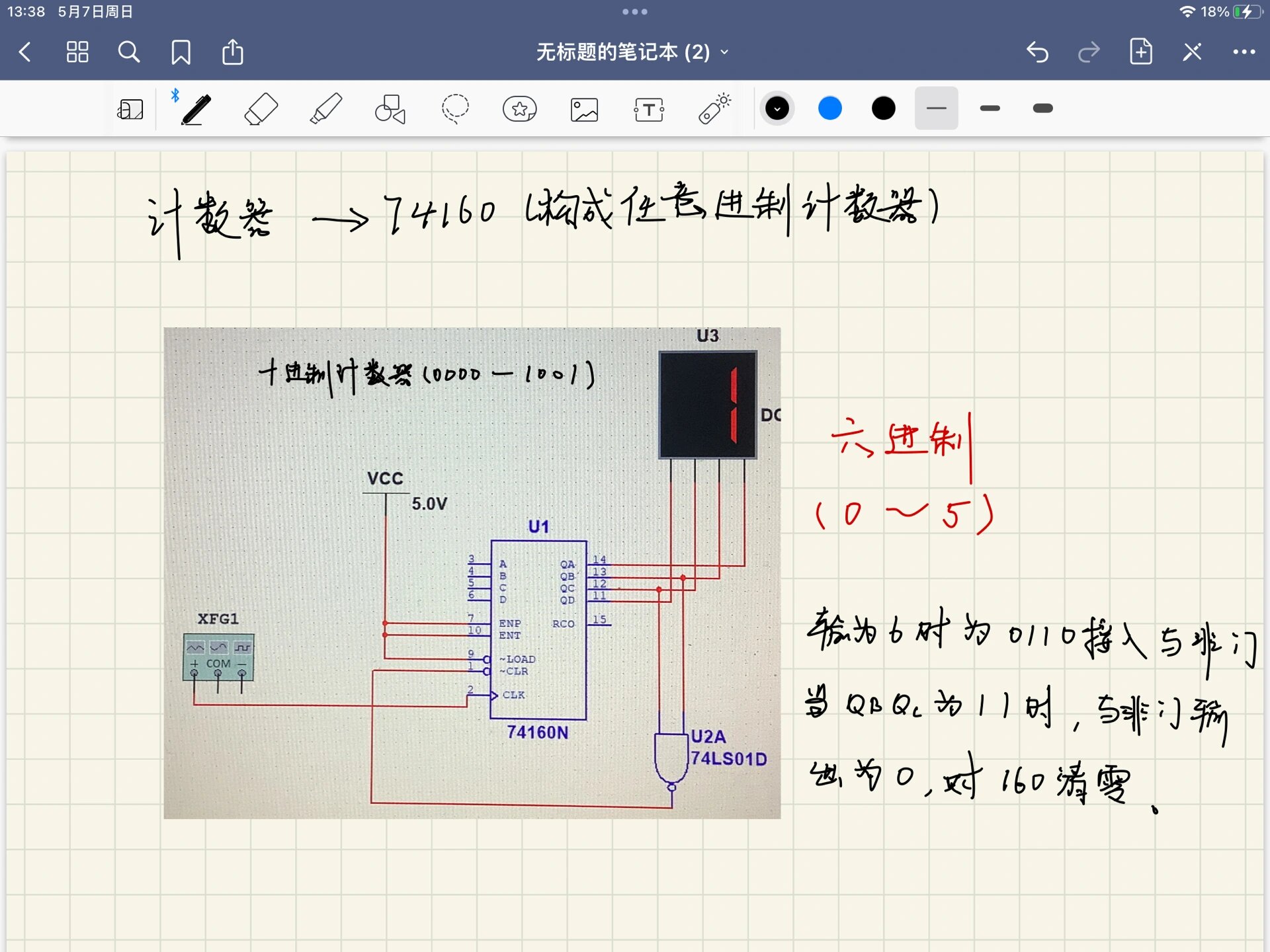

由同步十进制加法计数器74ls160构成一数字系统如图所

74ls00

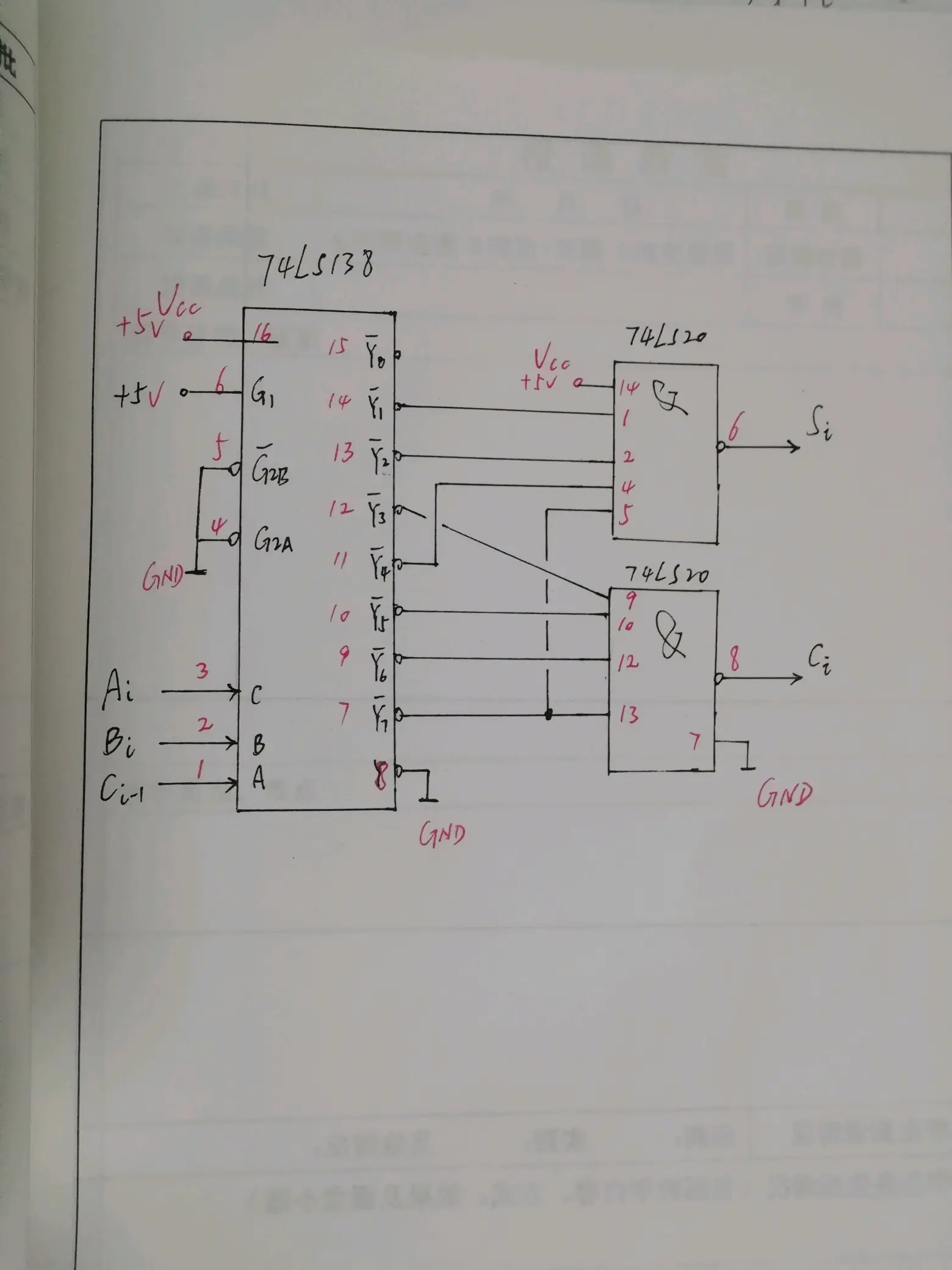

3 设计应用译码器的电路

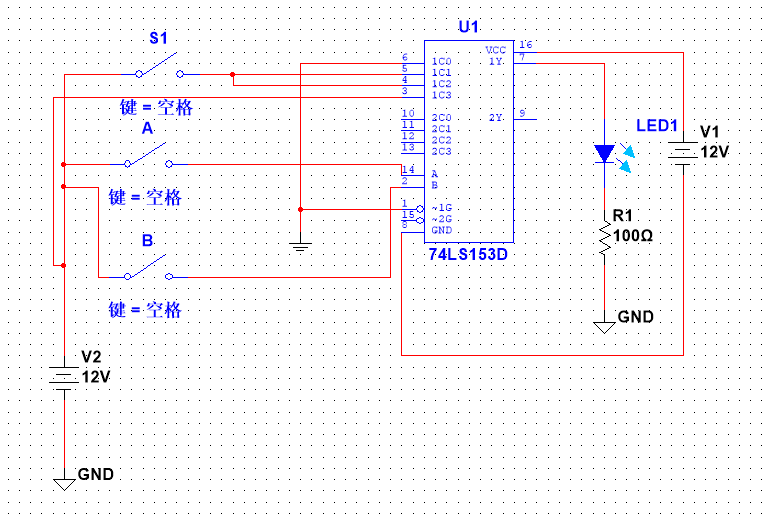

实验四 数据选择器④74ls153全加器

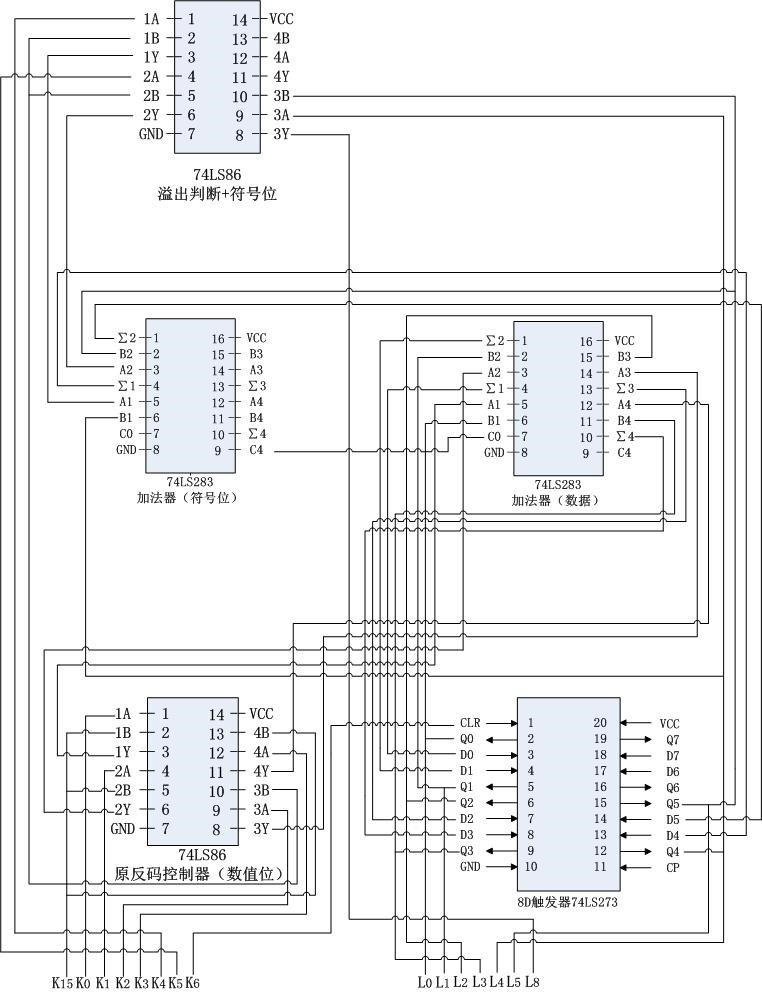

加法器用两片74 ls283 原

74ls00 图1

如何使用74ls00和74ls20设计全加器电路

74ls0074ls0874ls32全加器的ad原理图和pcb源文件

六

一位二进制全加器

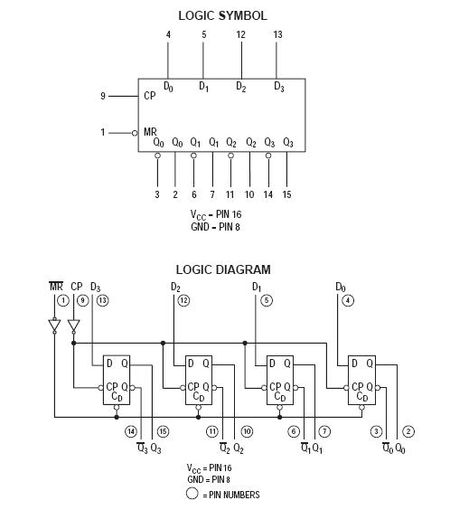

如何设计二进制同步加法计数器

74ls00

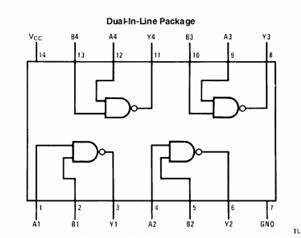

sn74ls00n 直插dip14 四路2与非门/逻辑ic 74ls00全新芯片ic电子

计数器之74ls160 作为十进制加计数器

用两片74ls160芯片设计一个的计数器

全加器设计思路

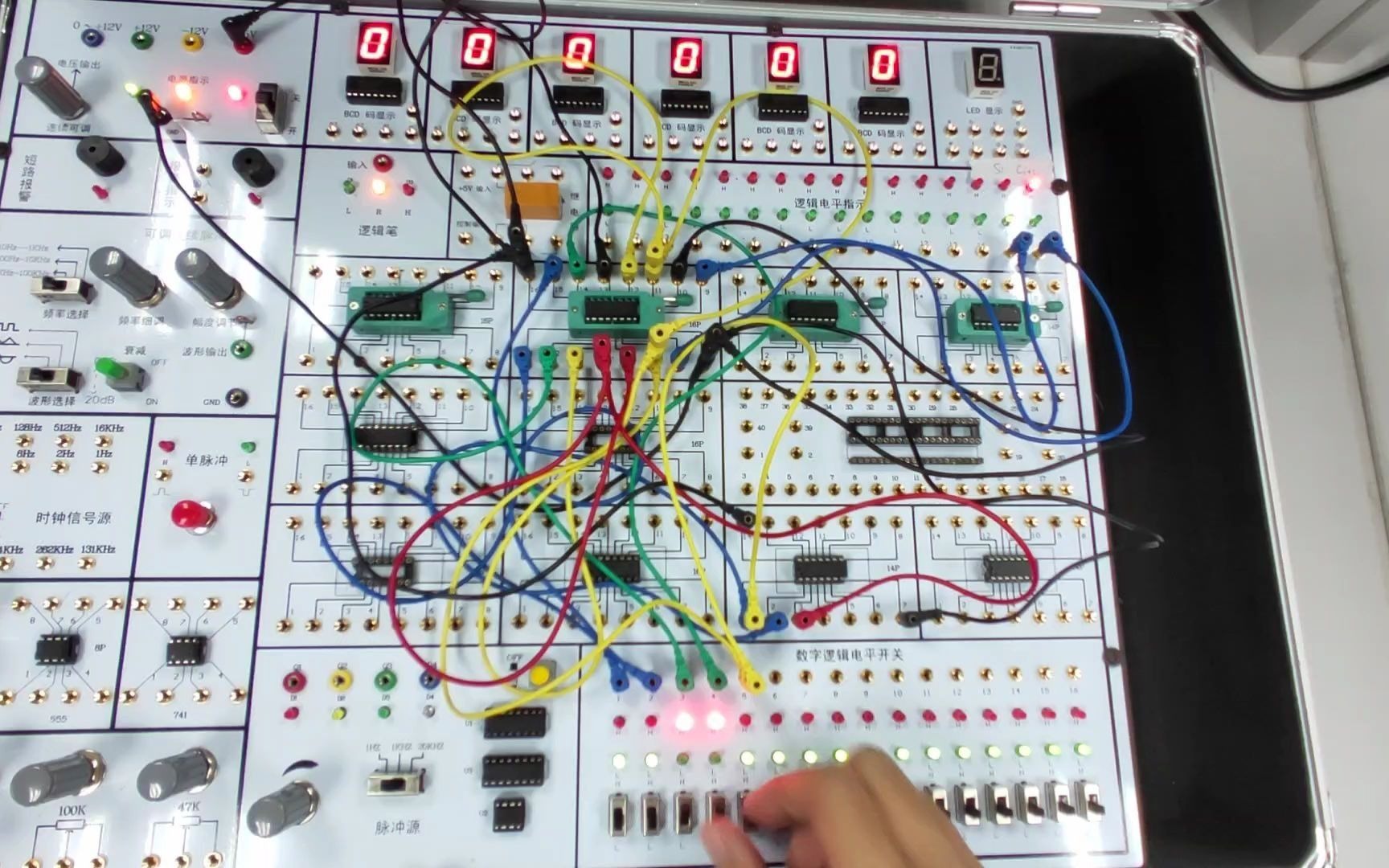

哈工大数电自主实验 数字钟的设计

有偶数个1

大学生活

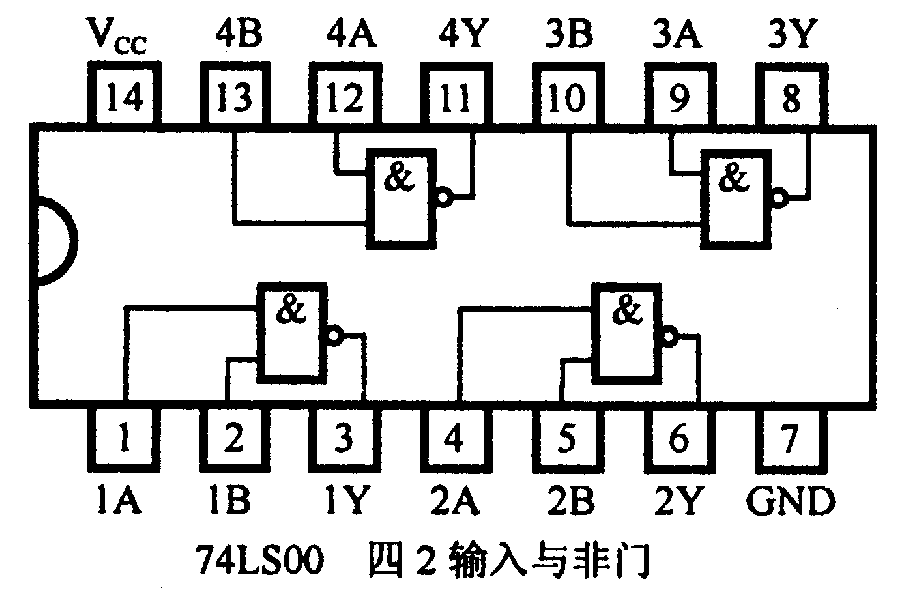

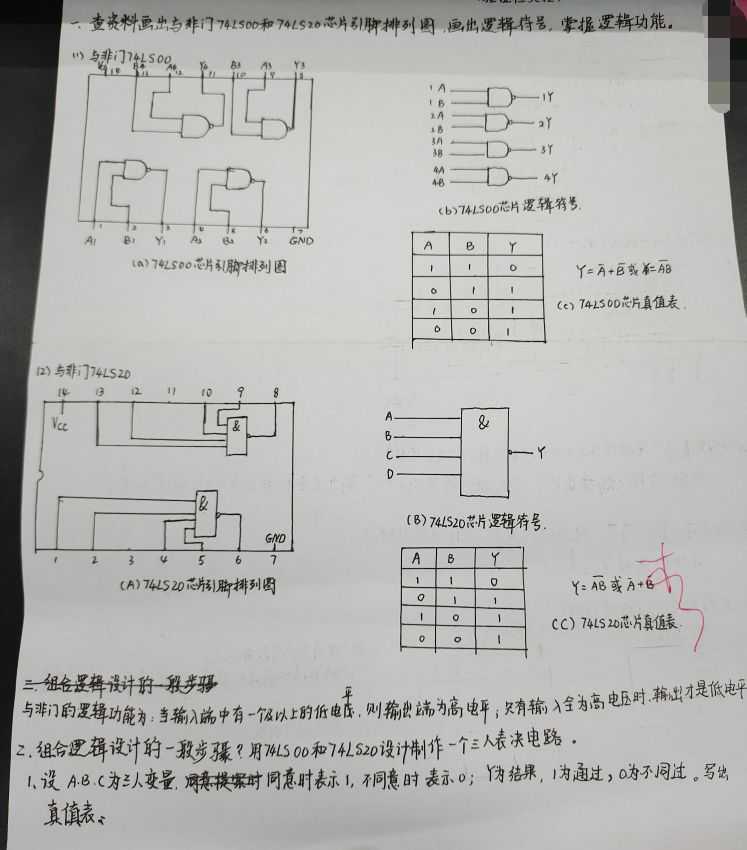

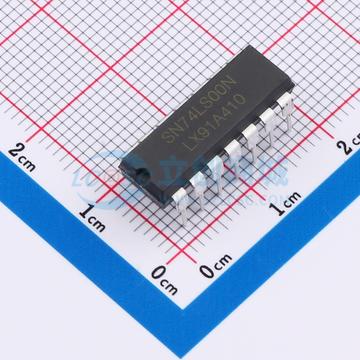

74ls20与74ls00逻辑门电路分析

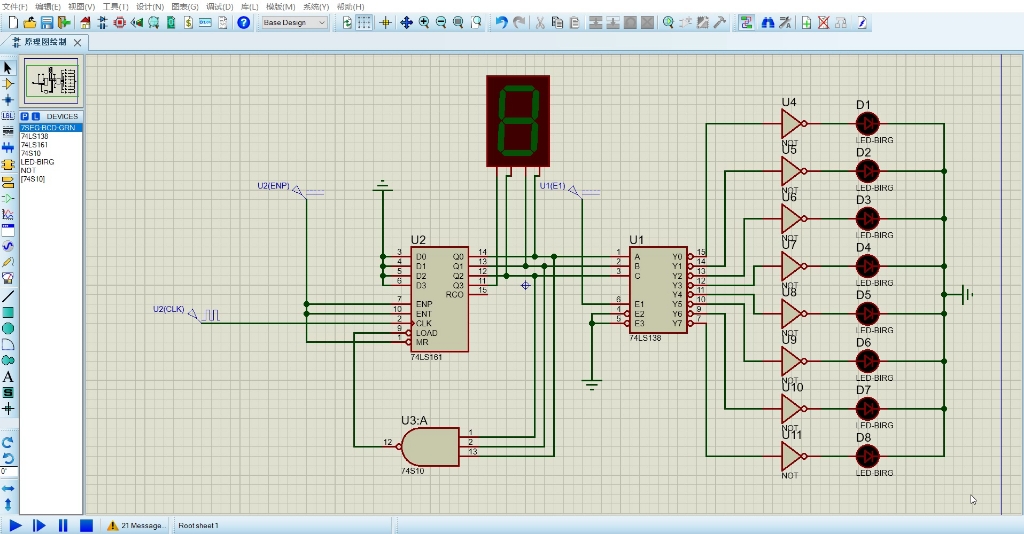

基于74ls161和38译码器的流水灯

2个74ls192和一个74ls00怎么构成24进制计数器

from chenxi组合逻辑电路

74ls00

用74ls00

千m以太网

数字电路实验 逻辑门与74ls00/20功能探索

二 实验仪器 数字电路试验箱;芯片74ls00 二输入端思与非门

电脑版 | 更新时间:2025-02-01 17:42:20