八位全加器

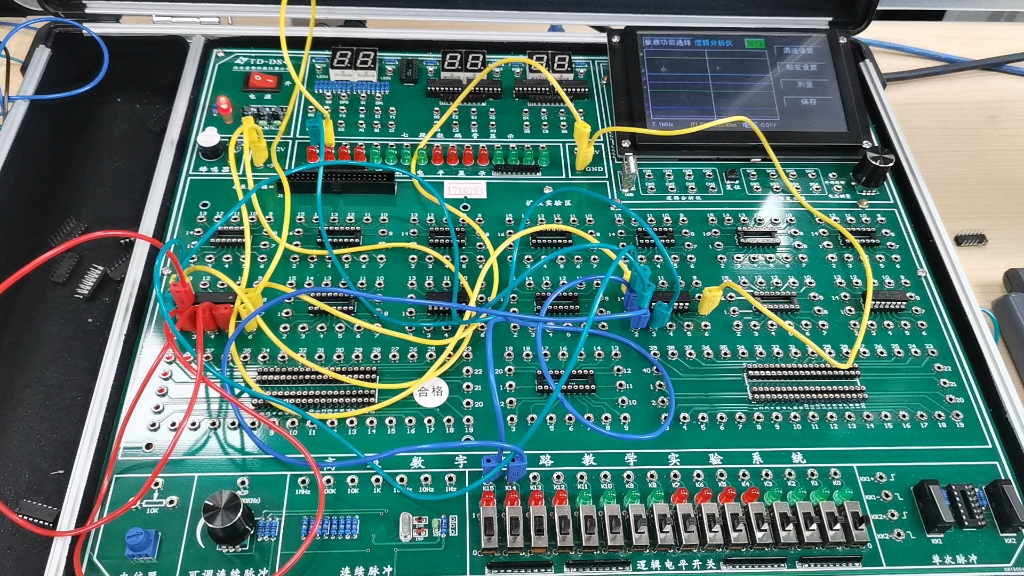

数电实验三 全加器应用 1

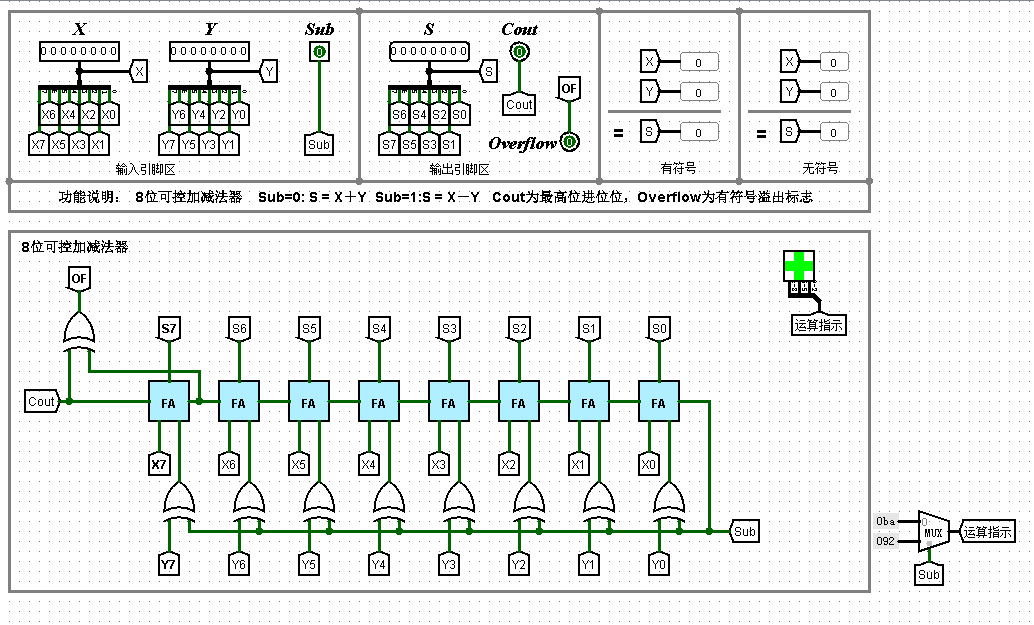

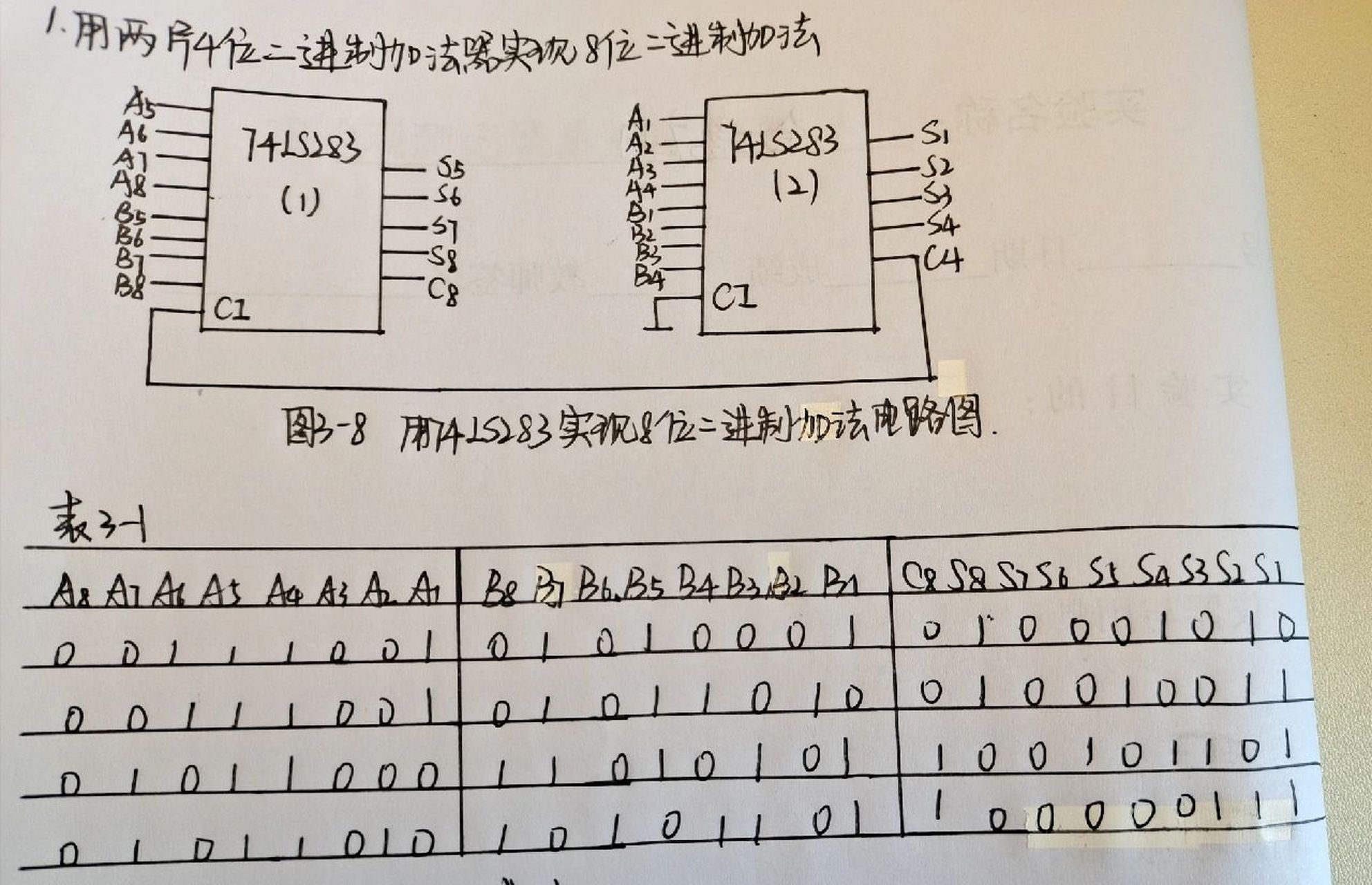

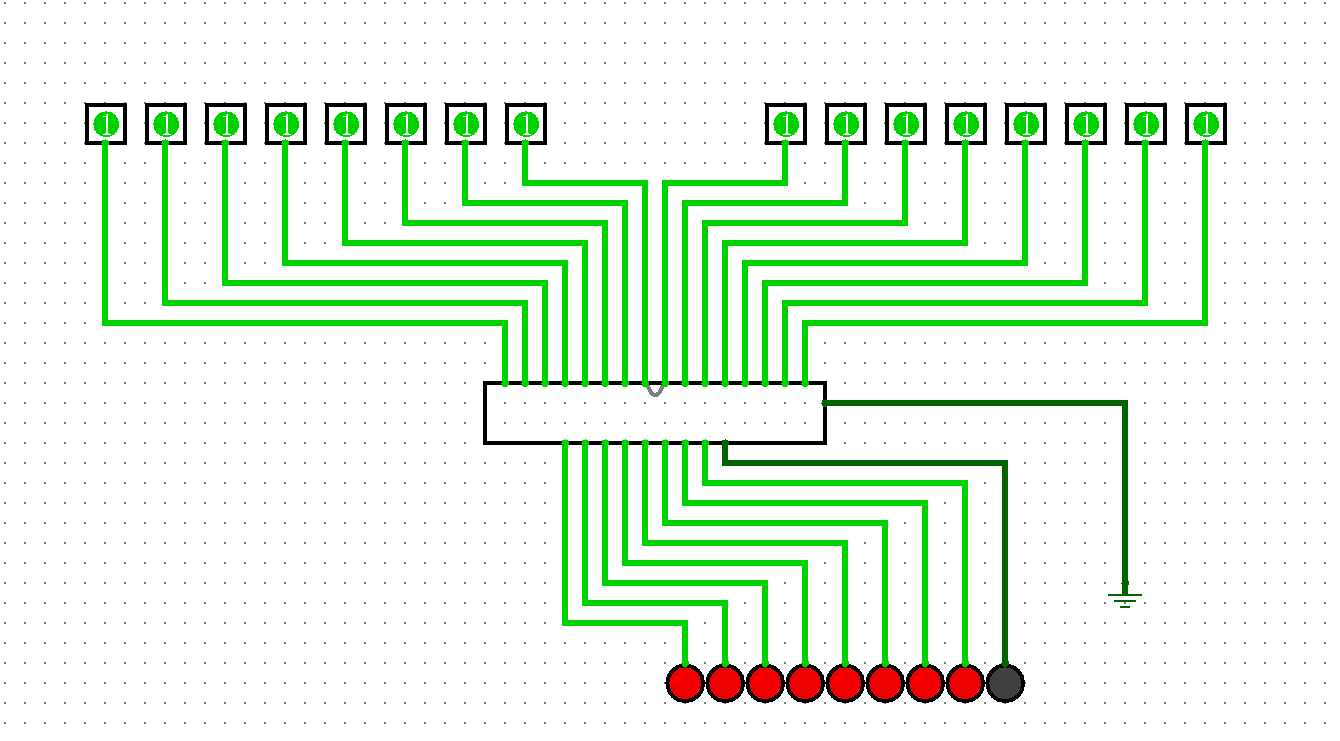

设计8位全加器

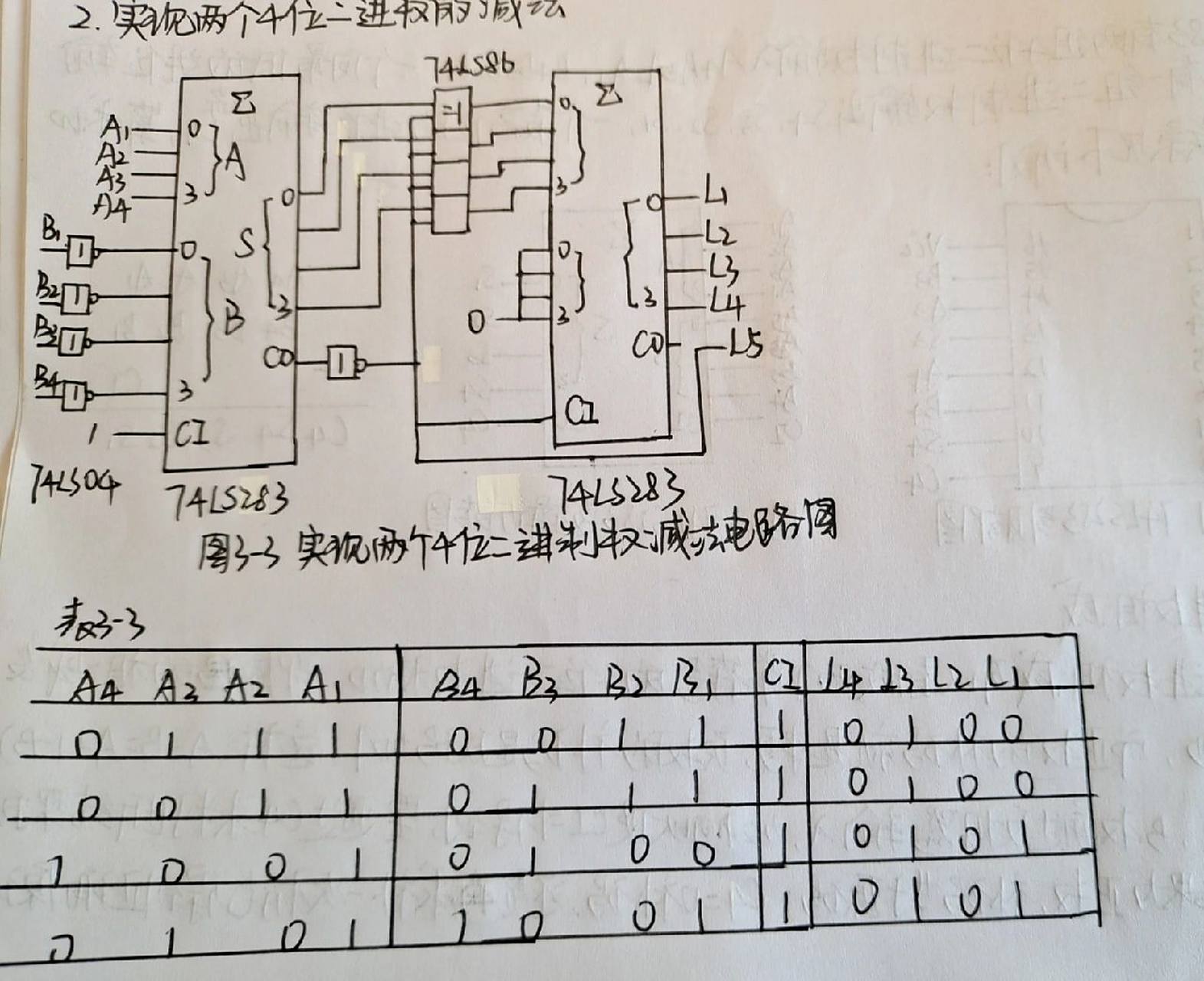

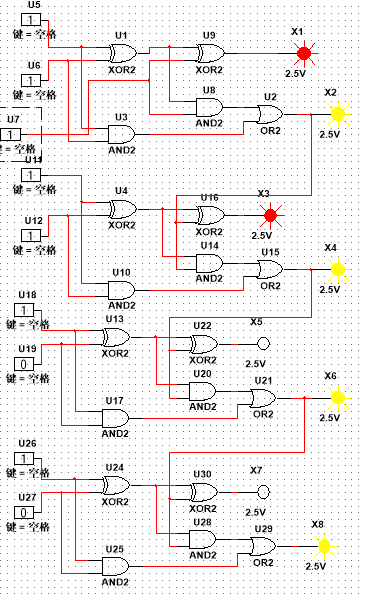

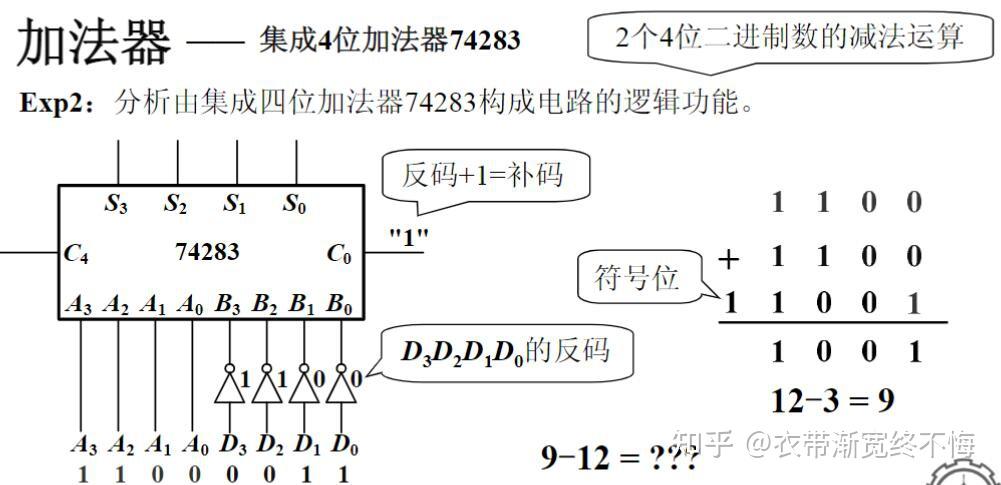

该实验通过全加器串行输入实现8位可控加减法

从零开始搭建一个8位计算机系列

八位全加器原理图设计实验报告

数字电路基础那些事2

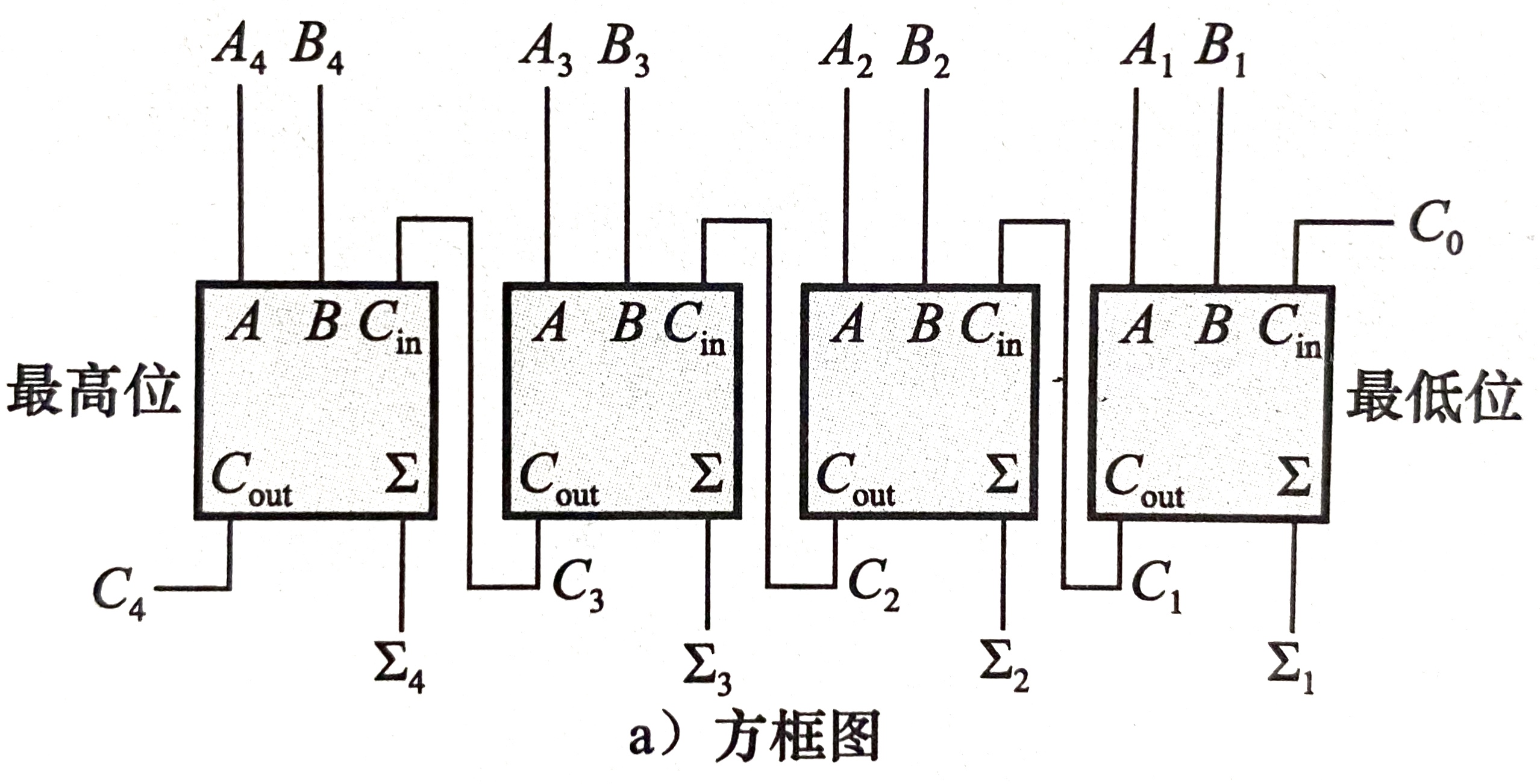

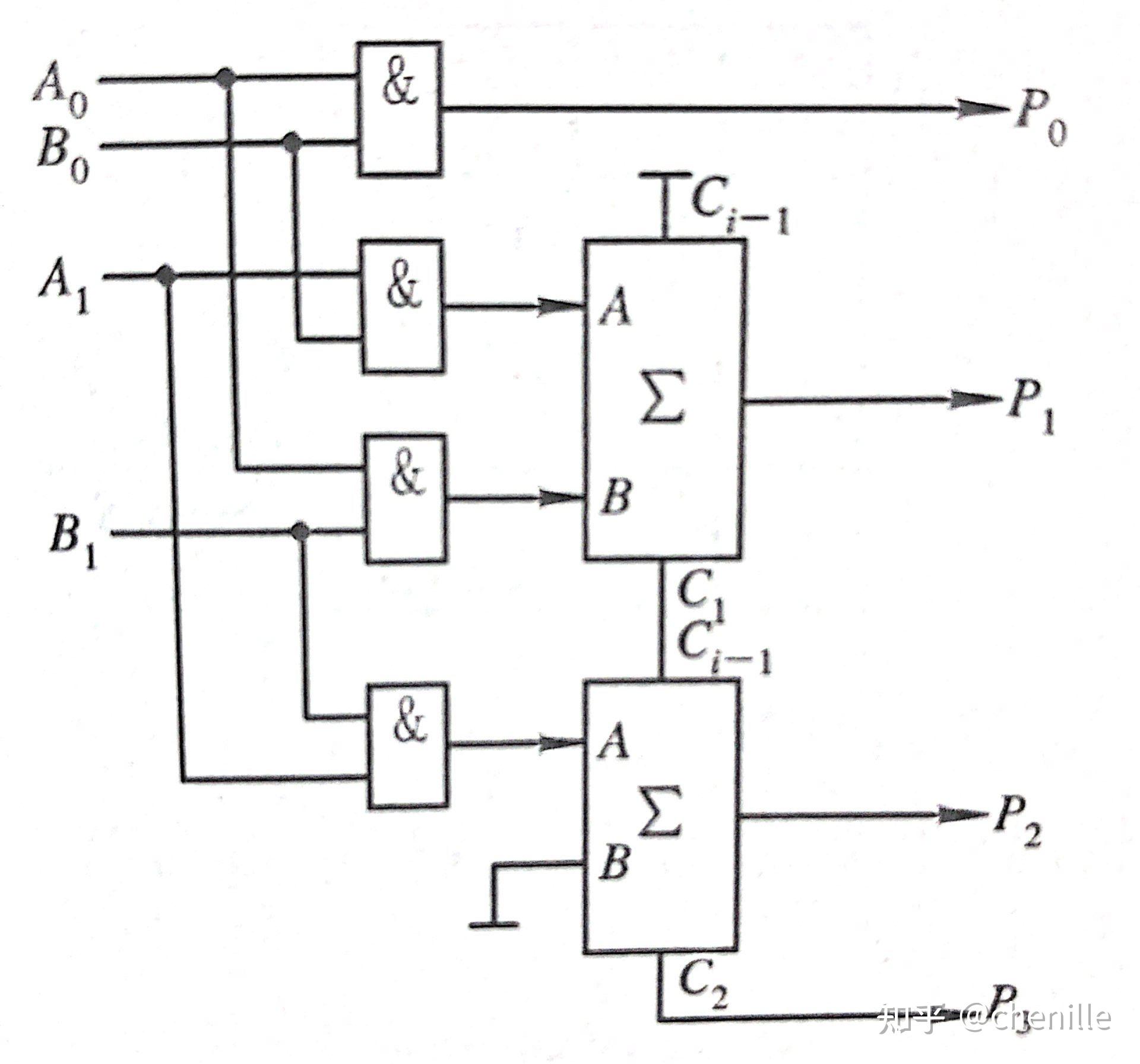

全加器实现的8位行波进位加法器

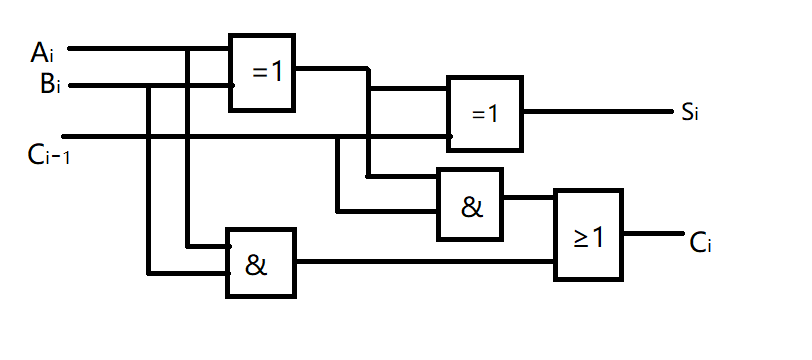

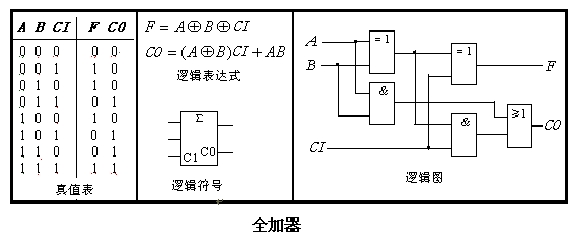

半加器和全加器

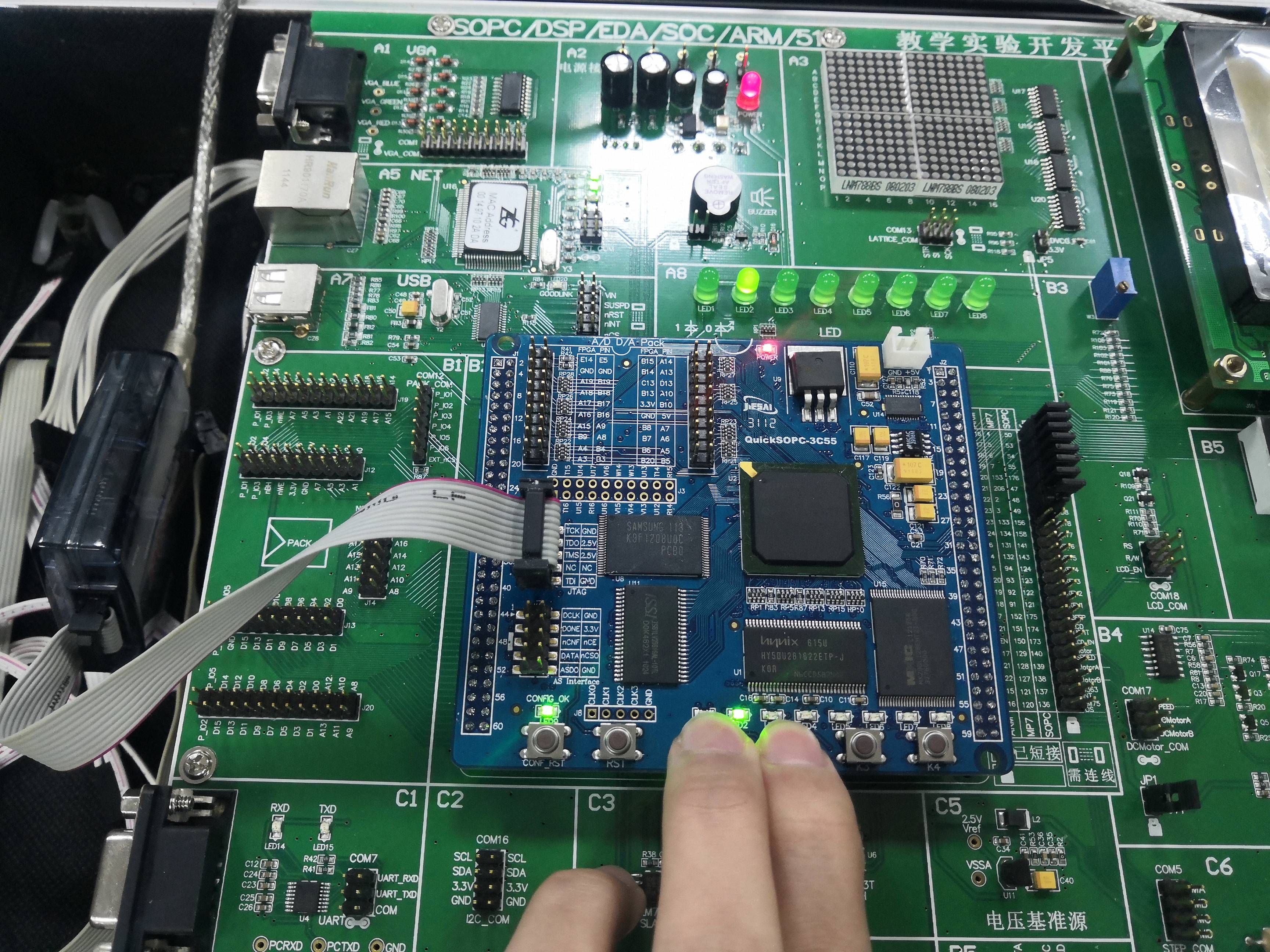

基于原理图的8位全加器层次化设计

思考题用verilog代码设计1位全加器module f

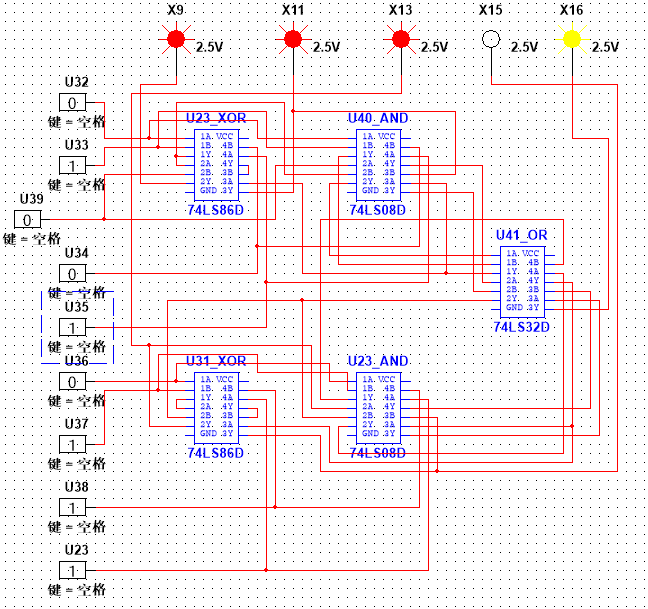

3 按照全加器电路图

实验二 8位加法器设计

数字逻辑实验 数据选择器的应用

数电实验三 全加器应用 1

八位加法器可以由7个全加器和1个半加器串联组成

利用与非门或异或门构成全加器

全加器原理介绍

从零开始搭建一个8位计算机系列二搭建4位全加器

全加器实验

fpga全加器

logisim实验

全加器真值表

3 全加器的应用

三

四位全加器 16进制数码显示 60进制计数器

quartusii四位全加器

全加器

在设计完成全加器之后

全加器

基于quartus完成1位全加器的设计及4位全加器的设计

电脑版 | 更新时间:2025-01-15 14:10:12