八位加法器

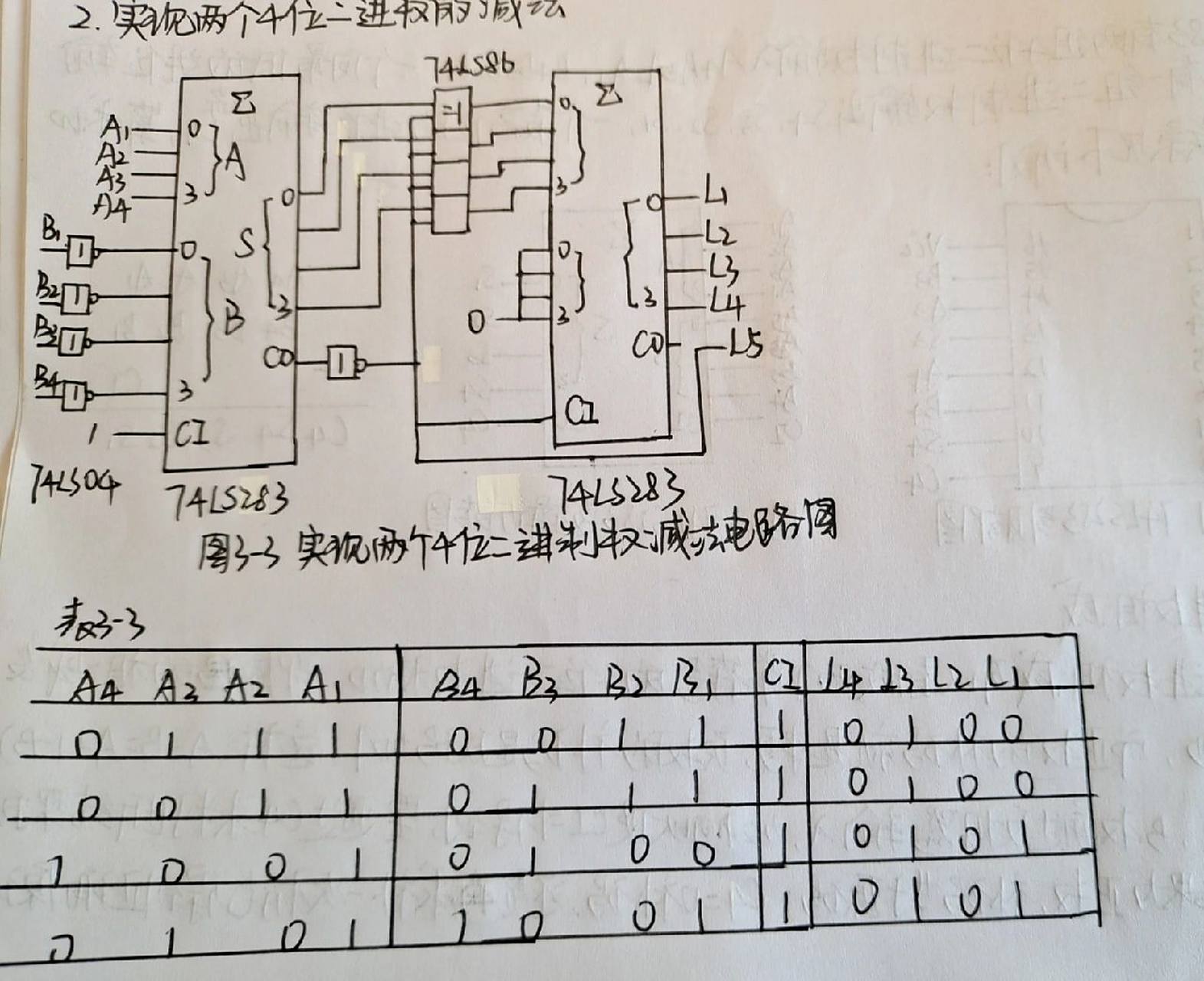

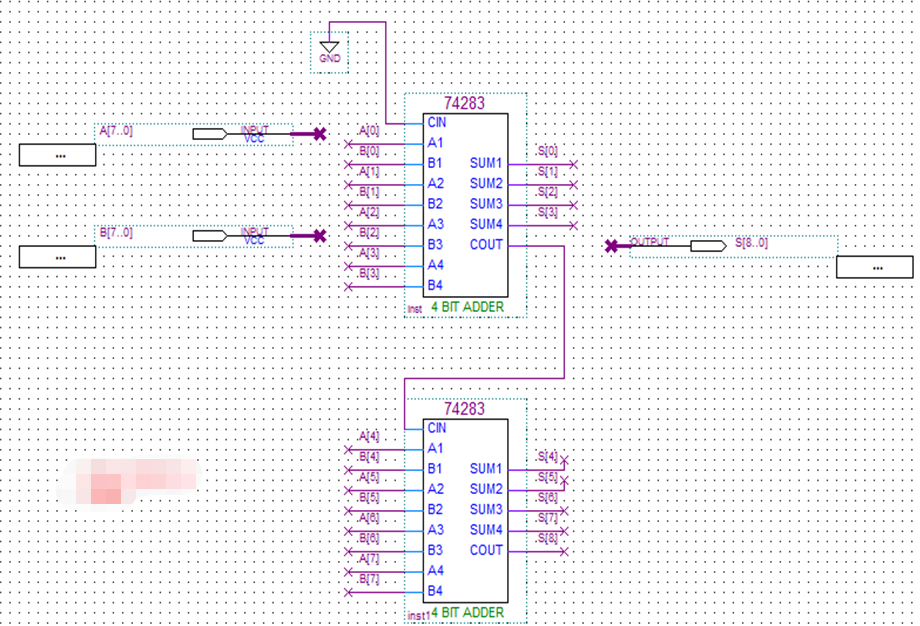

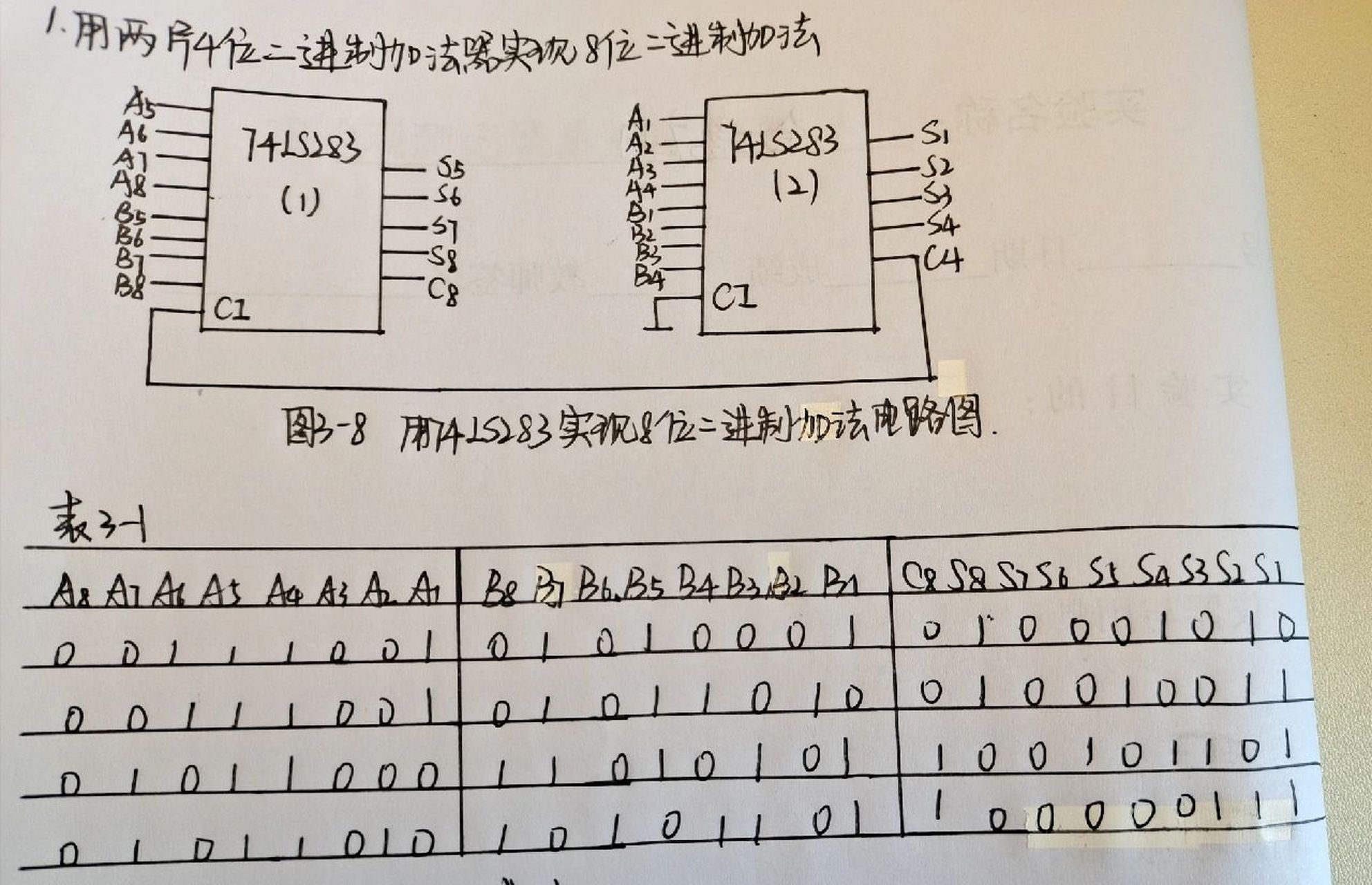

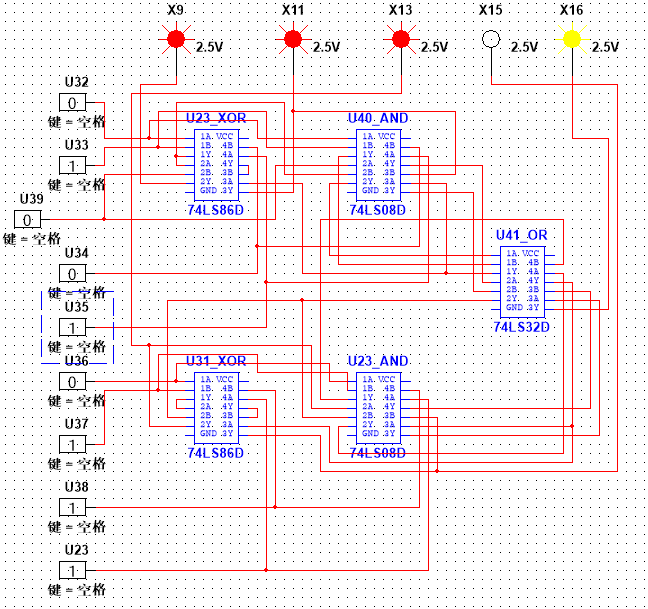

用两片4位二进制加法器实现8位二进制加法 电路图如p1所示

八位加法器

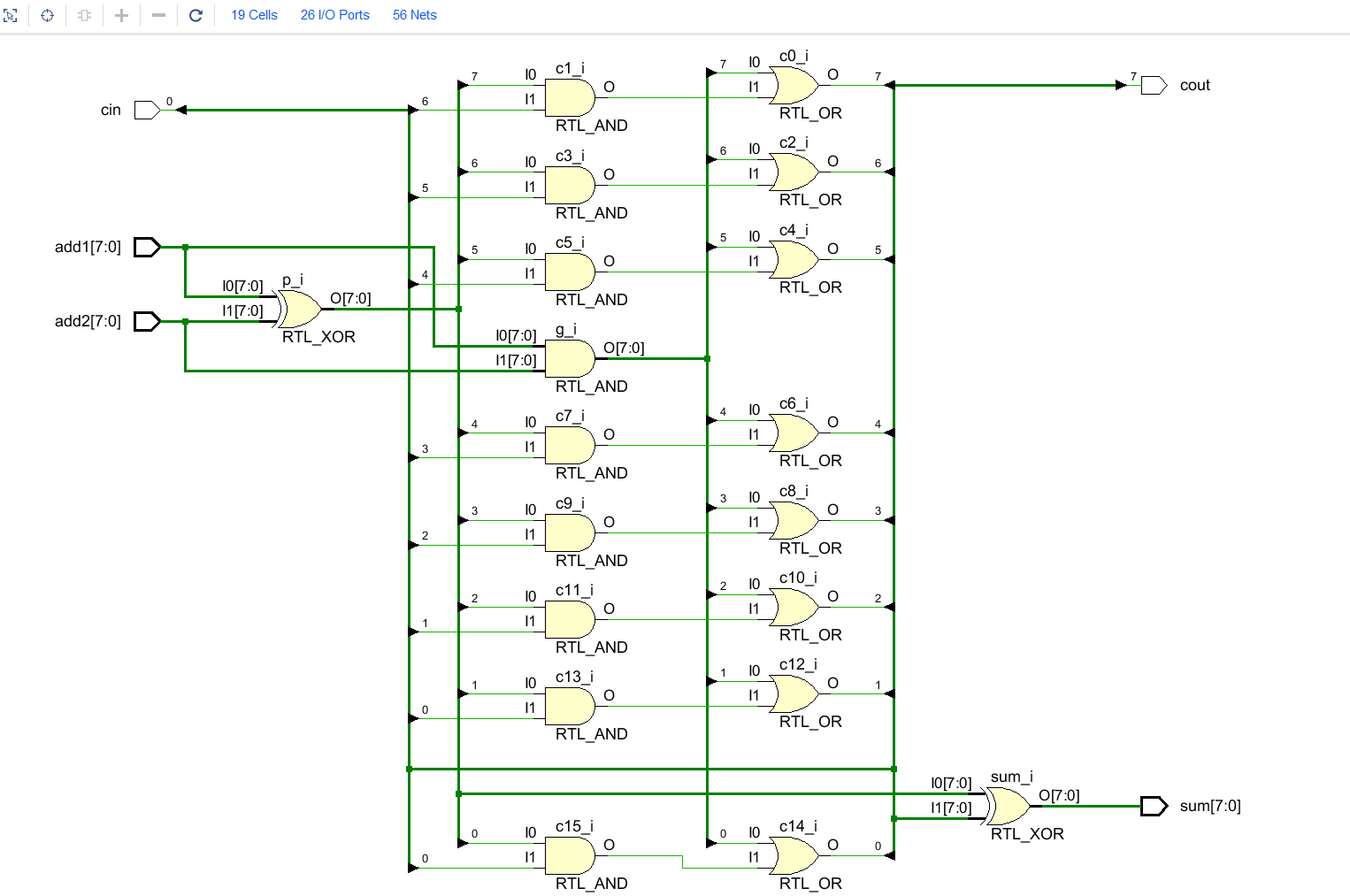

八位 kogge

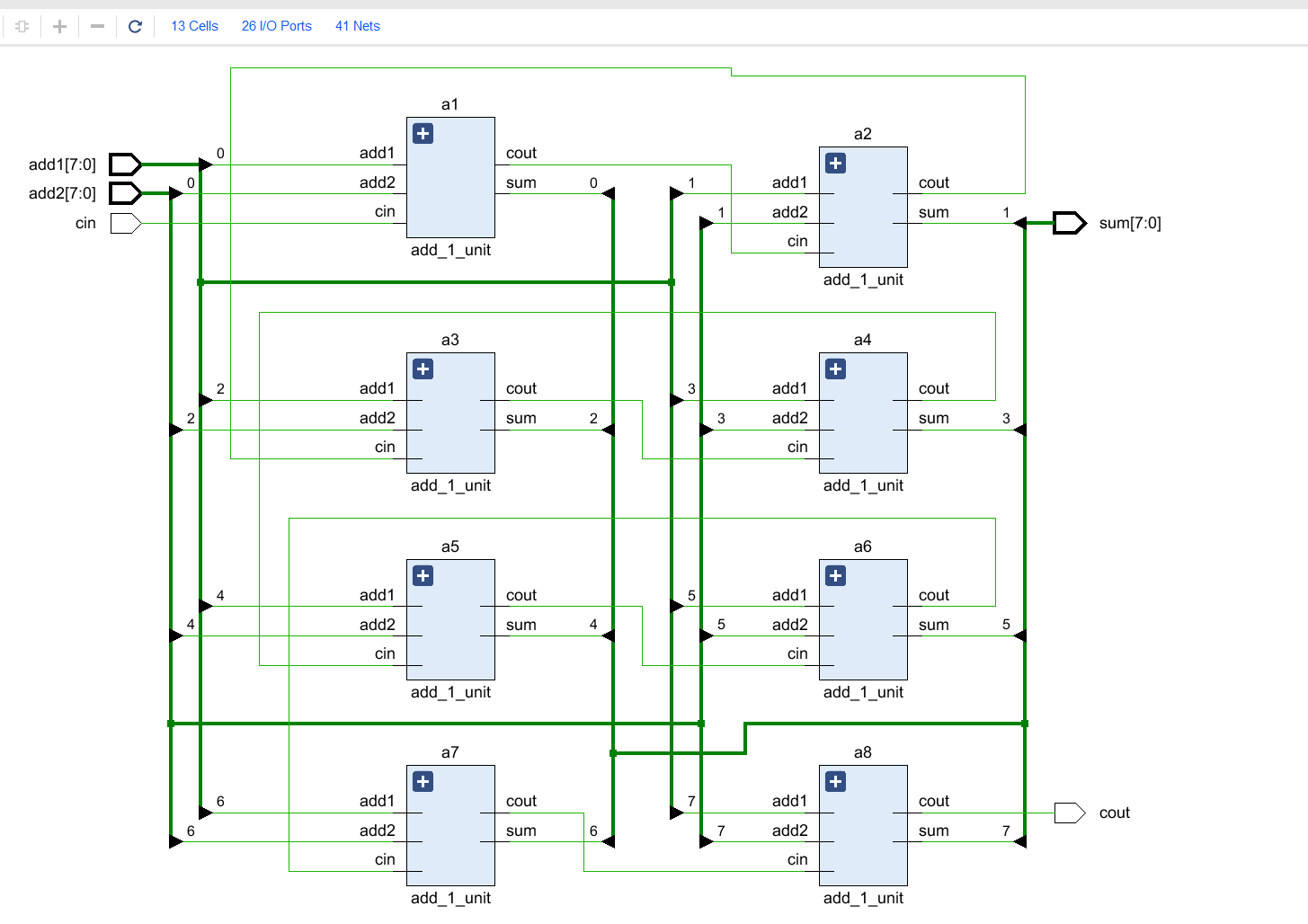

8位并行加法器的设计

基于vhdl语言的8位加法器的设计

八位加法器

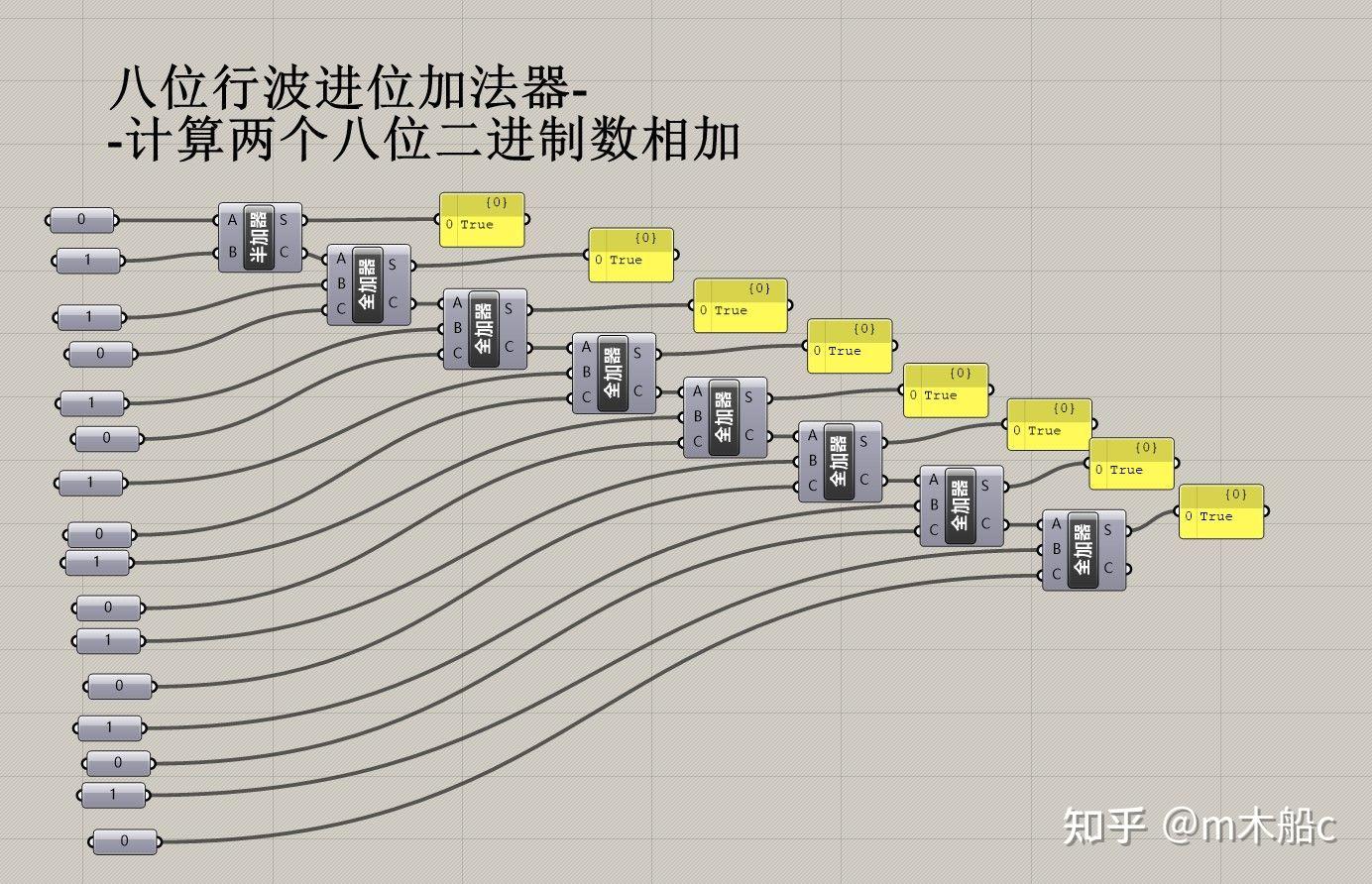

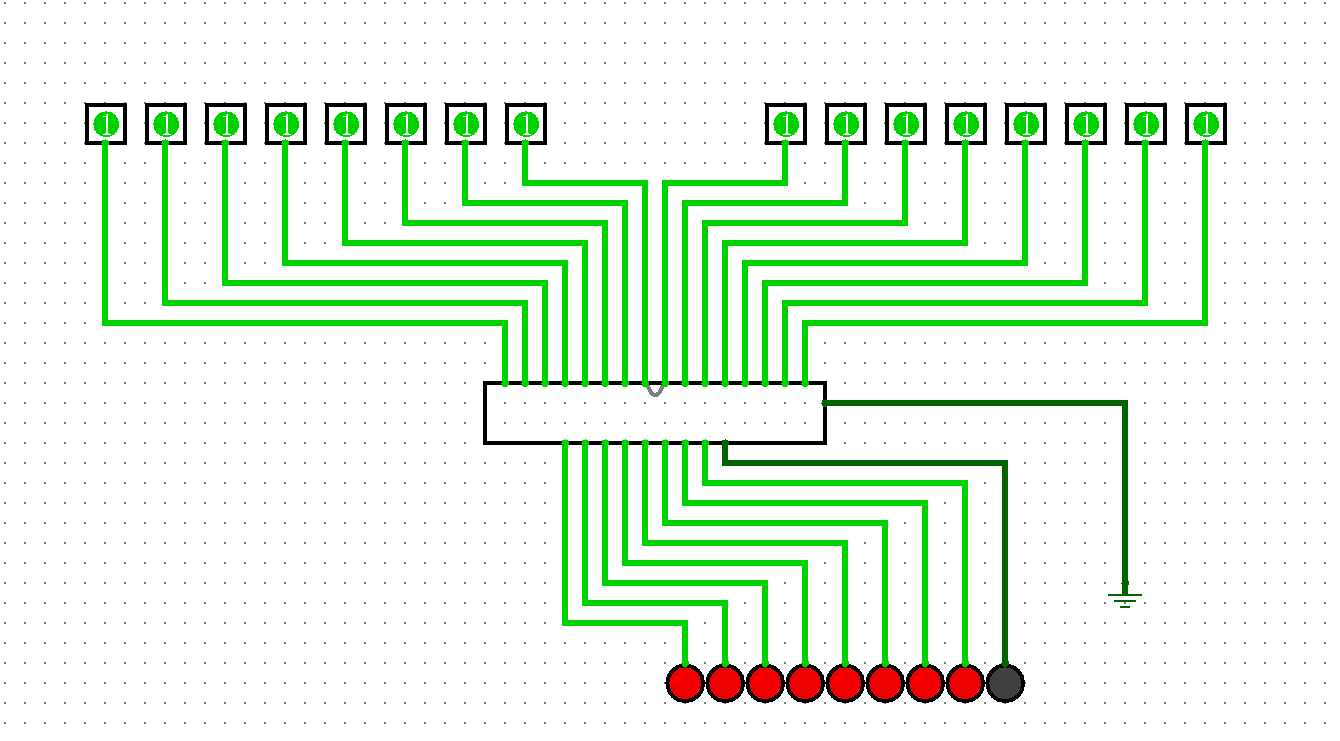

计算机组成原理 八位串行加法器实验

八位超前进位加法器八位行波进位加法器

21级计组硬件实验三

fpga八位加法器

八位加法器可以由7个全加器和1个半加器串联组成

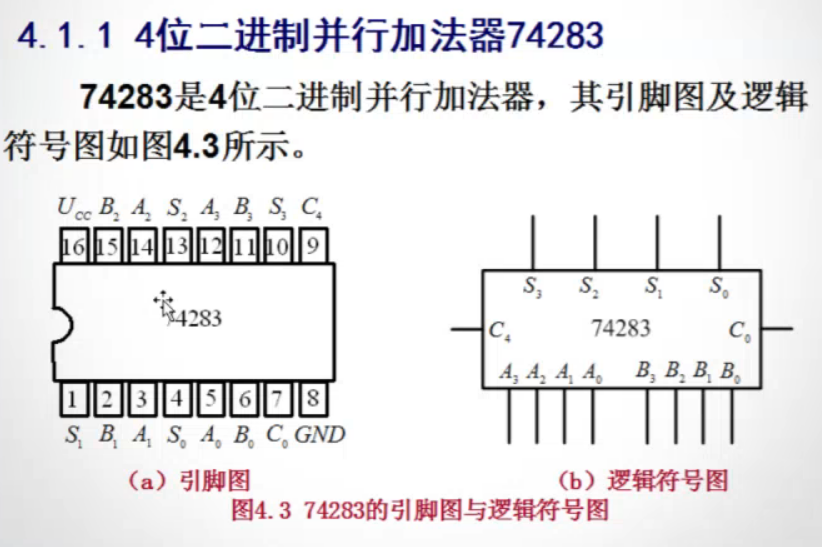

1 4 8位加法器

这是为了验证二进制加法器可以使用

串行进位和先行进位加法器 部分booth乘法

fpga综合实验018位加法器的设计

第8篇 串行进位加法器

实验二 8位加法器设计

用两片4位二进制加法器实现8位二进制加法 电路图如p1所示

八位加法器

八位超前进位加法器八位行波进位加法器

八位加法器的设计实验报告

八位超前进位加法器八位行波进位加法器

八位二进制加法器

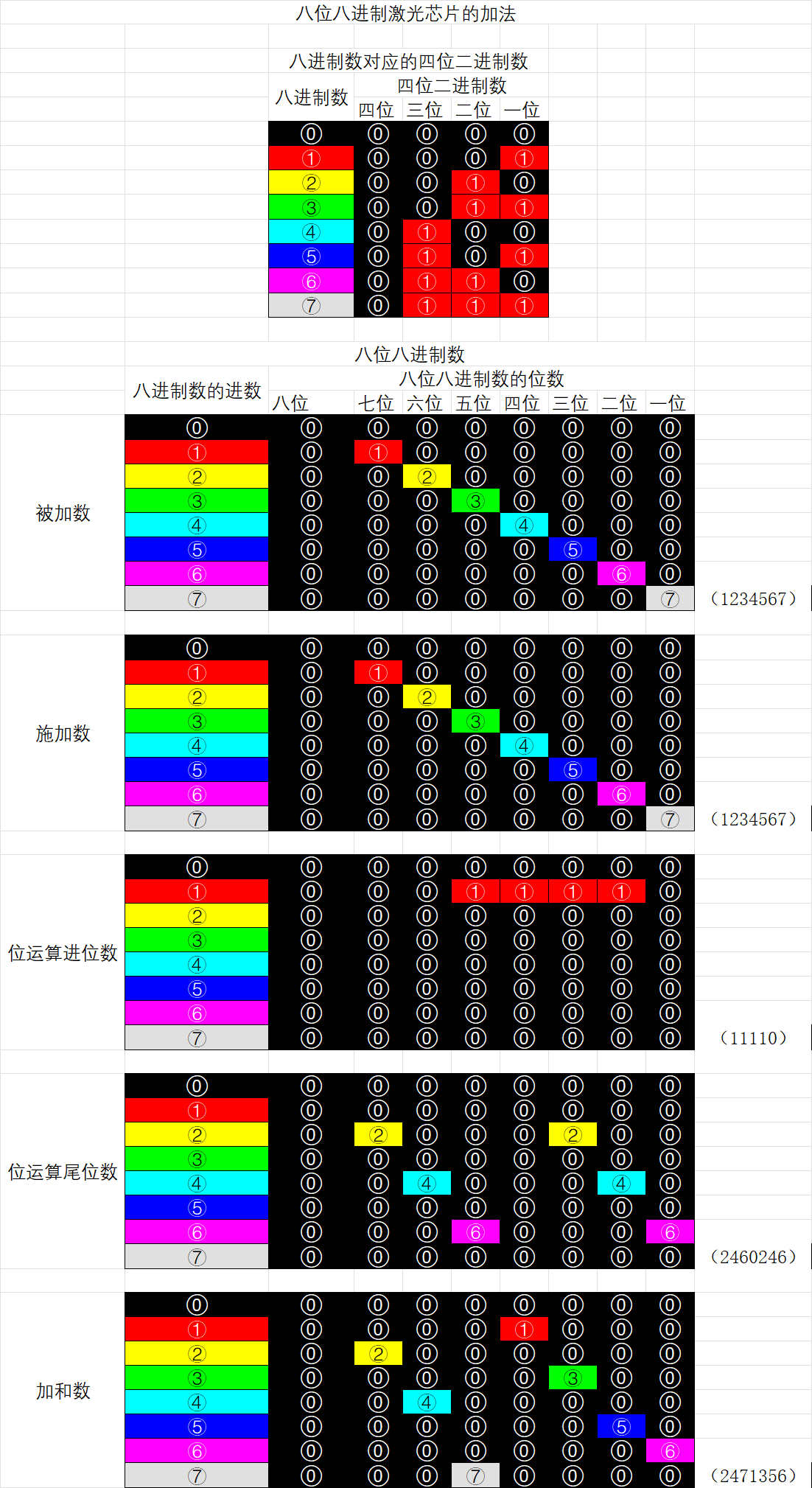

8位8进制激光加法器的简化模型

从零开始搭建一个8位计算机系列

八位串行加法器

《编码 隐匿在计算机软硬件背后的语言》

全加器实现的8位行波进位加法器

四位二进制841bcd码加法器 doc

41加法器

电脑版 | 更新时间:2025-01-15 07:55:55